--------------------------------随便写写,思绪走到哪里就写到哪里吧-----------------------

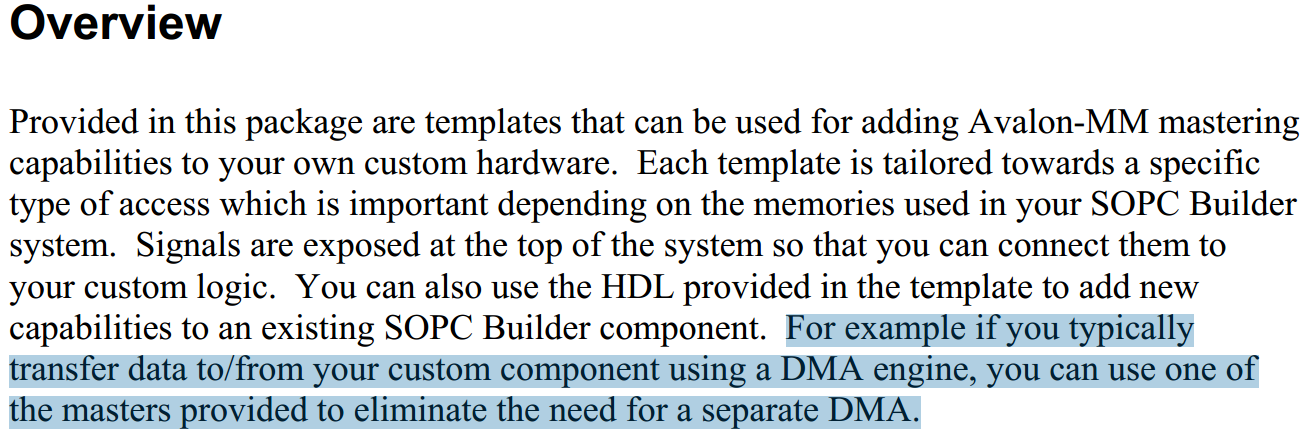

一。应用背景:在NIOS中对于数据流的处理,比如通过C操作内存,然后通过该总线对内存中的数据流做处理。常规的例子比如,视频流的处理。本文的目的记录文档中的比较关键的点。欢迎大家一起交流,Q群:912014800。

二。在intel fpga 可以查到该IP,手册中可以看到如下所示介绍:

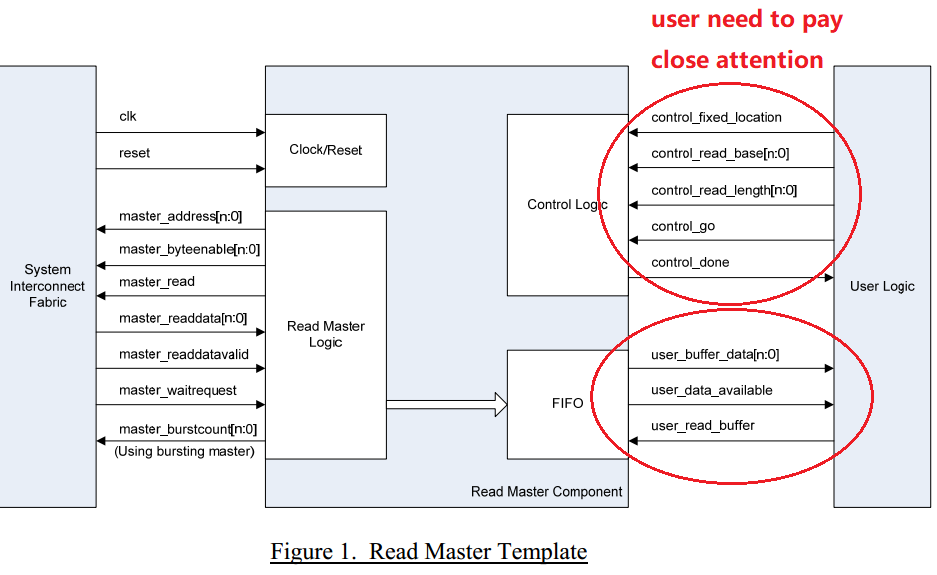

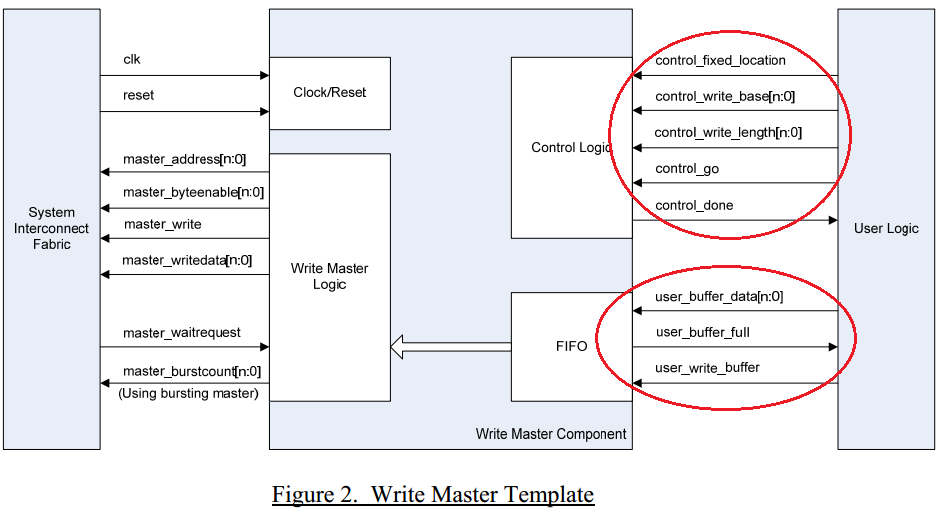

接着可以看到如下的框图:

其中红色的圈需要自己verilog,左边的部分在qsys中自行连接即可,比如连接打到一个sdram模块。

接下来我们看看信号定义:

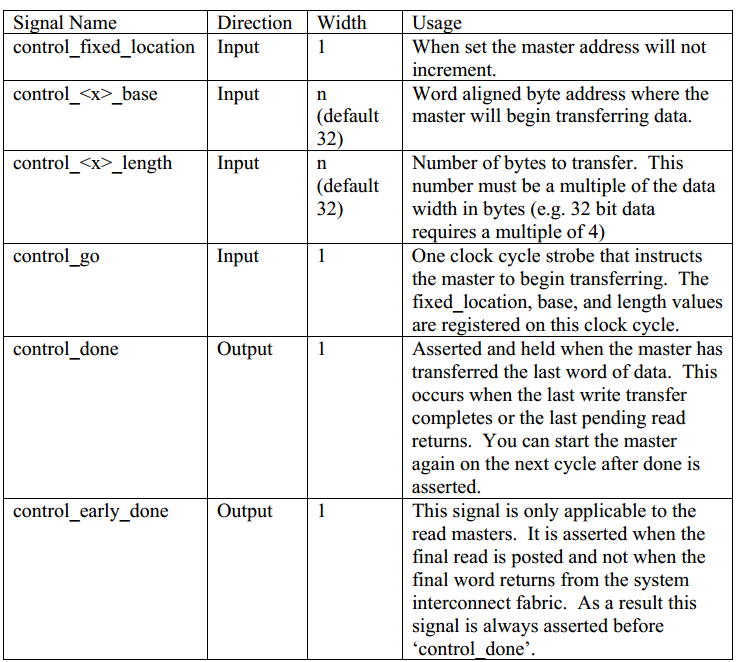

(1)控制信号

control_fixed_location :设置为1,地址不能增加,一般传输很多数据请设置为0

control_(x)_base:基地址

control_(x)_length:长度,以byte为单位。比如我设置的为8,则读两次,每次读取4byte数据。

control_go:一个clk表示起始,

control_done:最后一个数据已经读出来了。user可以在检测到该信号后,再产生go信号,依次读取。

control_early_done,:仅对读有效,当最后一个数据已经贴出,而实际并没有从内部读到fifo,该信号拉高,因此该信号总是超前done信号。

(2)读信号

user_read_buffer:当user需要寄存数据拉高就行了,在下一个时钟,数据才有效。

user_buffer_data:当user_data_avaliable有效时,则在其下一拍表示该数据有效,也就是第一个有效会有延时一拍。

user_data_available: 什么意思呢?当缓冲有有效数据时,该信号就为1。当这个信号为0时,你不能操作user_read_buffer,否则就完蛋。[就是这样]

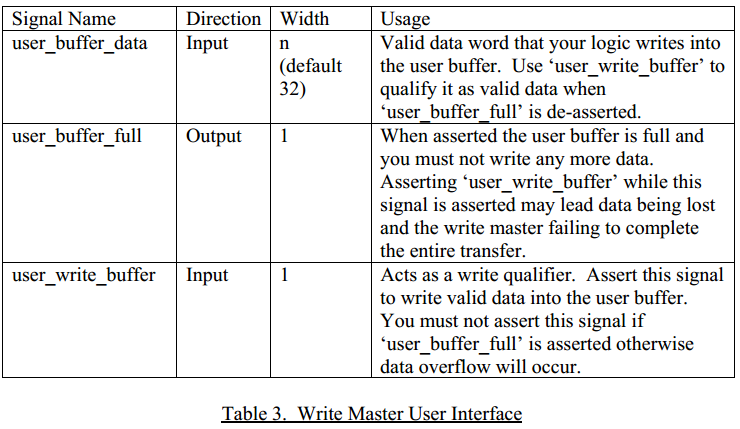

(3)写信号

user_write_buffer:数据有效指示

user_buffer_data:数据

user_buffer_full:当该信号为1时,你不能再写数据了。否则就完蛋