引言:工欲善其事必先利其器,欢迎大家一起交流,Q群:912014800。

在fpga学习中,熟悉一个工具的使用是很有必要的,可以加快开发进度或者帮助我们更好的定位问题。本文总结一些quaruts的常用技巧以供大家参考,不是非常全面,如有更好的技巧,请留言讨论。

使用版本:quartus prime standard 17.1 (win 10建议装15.0版本以上的,因为低版本的NIOS使用会有bug)

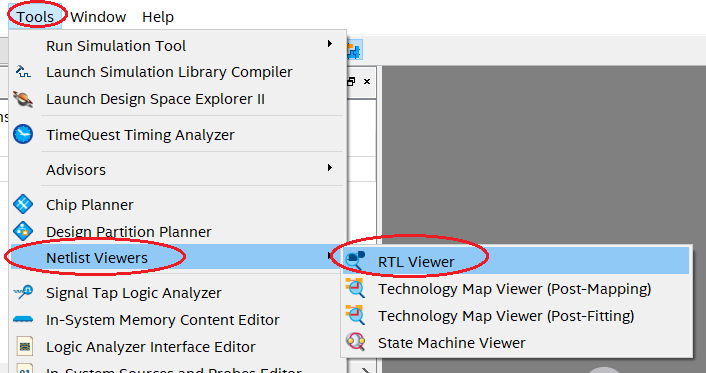

(1)查看RTL view(可以查看综合后的视图,可以帮助分析错误以及建立整个工程的架构)

1)方法一

2)方法二

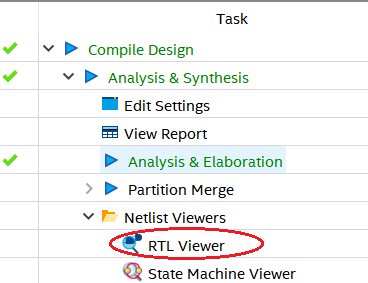

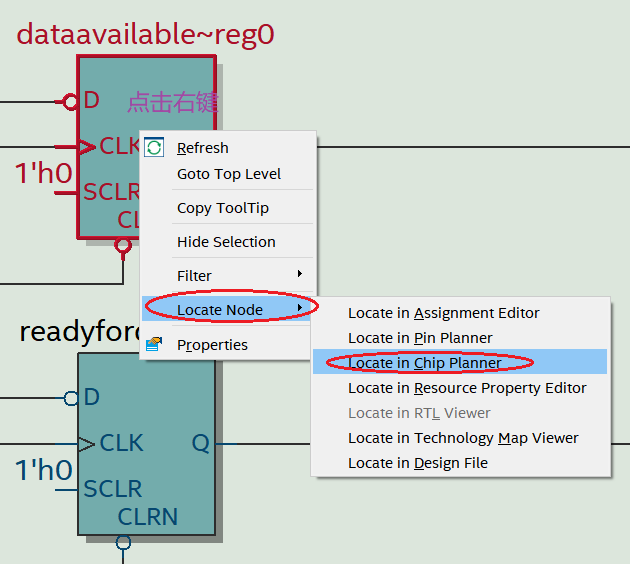

(2)查看chip plan(可以查看最终fpga怎么实现逻辑)

第一步:

第二步:之后会看到这个:

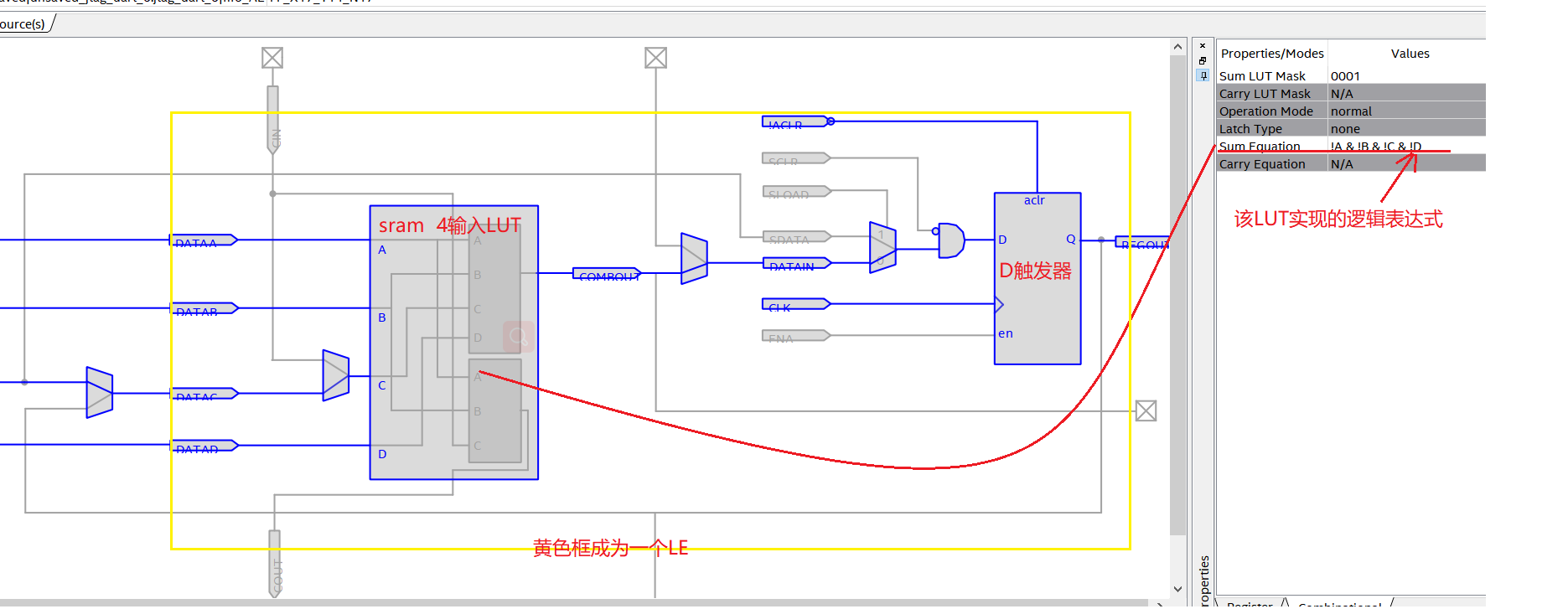

第三步:双击上图的蓝色块,然后会看到最终fpga实现的方式(注:高端器件可能是6输入lut或者两个6输入lut,且D触发器(有时候称为FF)不止一个):

(3)一个工程加入多个编译选项(我们在开发的时候用的是资源比较大的fpga,而实际产品是一个资源比较小的fpga,则需要多个编译选项)

正常状态下,编译选项(我的叫法)只有一个,如下图所示:

有时候需要在两个器件上综合同一份代码,那么应该怎么办呢?

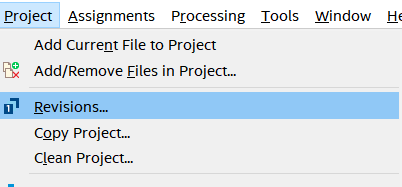

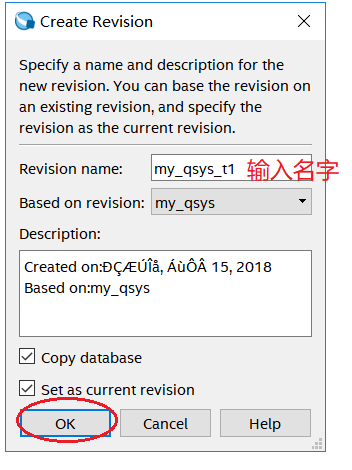

第一步:

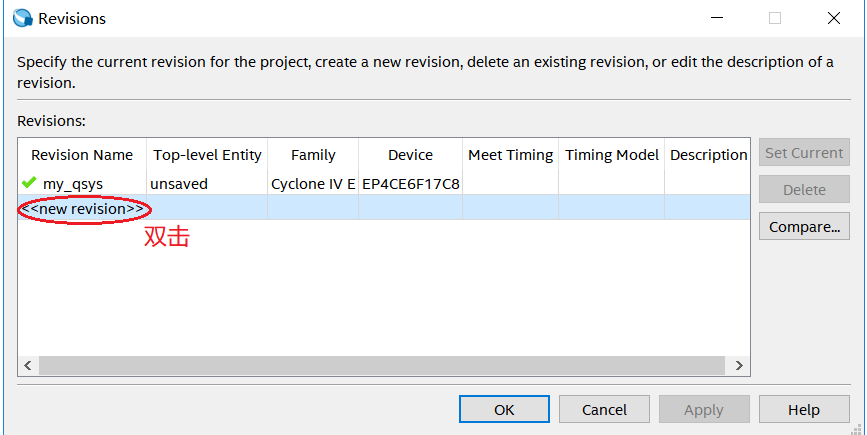

第二步:

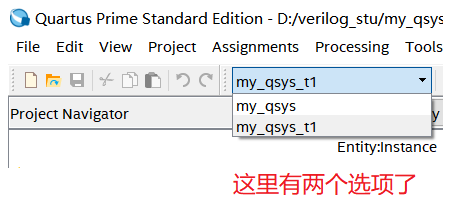

第三步:

第四步:

第五步:选择my_qsys_t1,然后如图5操作,之后便可以在另一个器件上综合了。

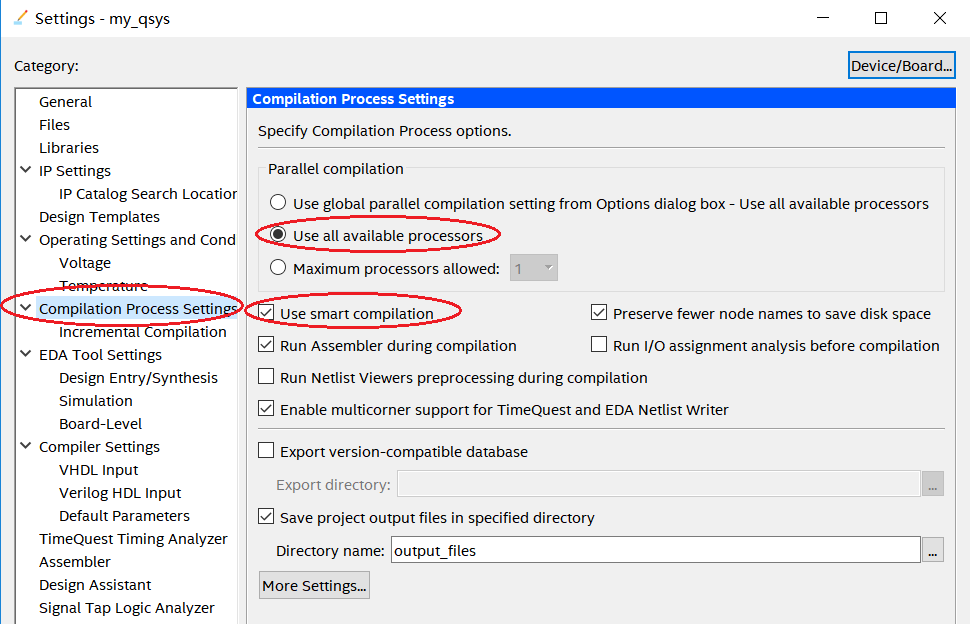

(4)smart 编译(快速智能编译),可以提高编译速度

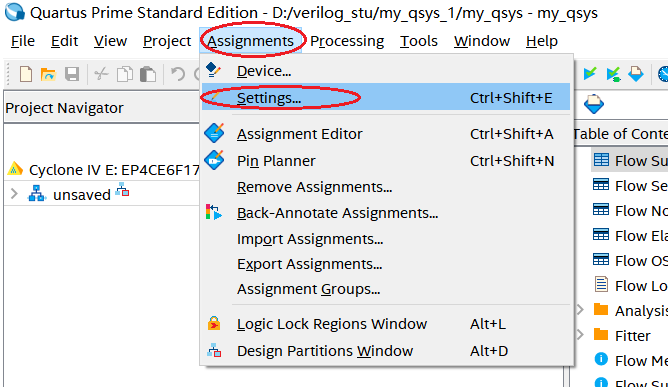

第一步:

第二步:

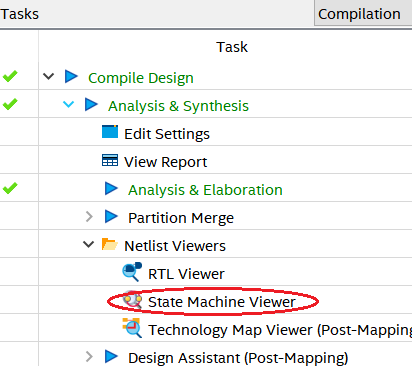

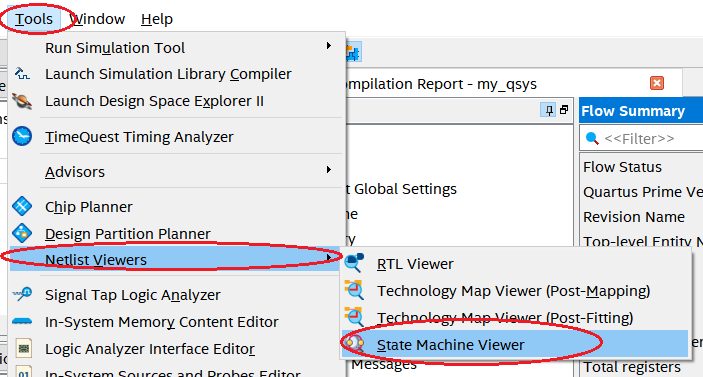

(5)查看状态机

方法一:

方法二:

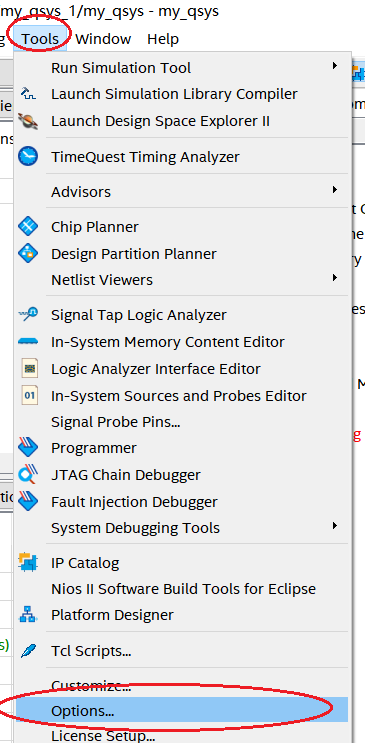

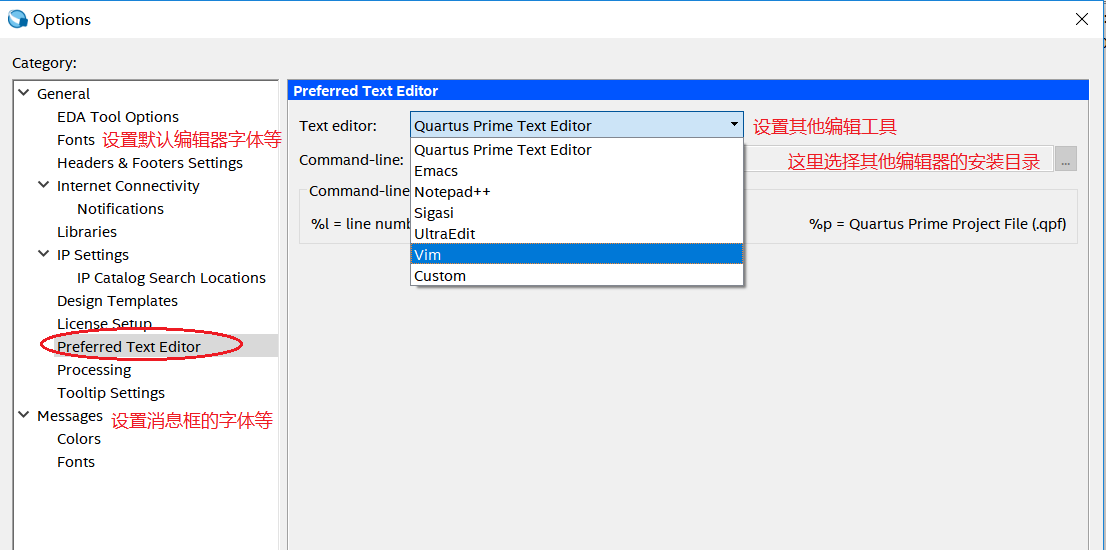

(6)设置字体,调用第三方编辑器(自带的不好用或者其他原因)

第一步:

第二步:

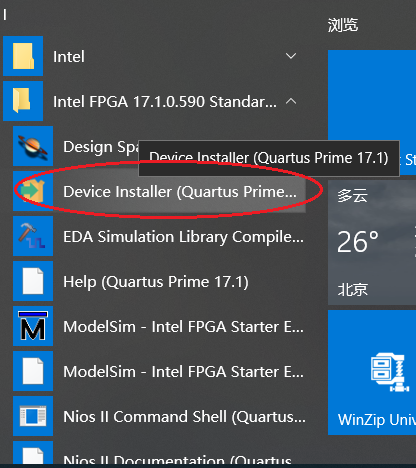

(7)安装器件库(用其他器件发现没有库怎么办)

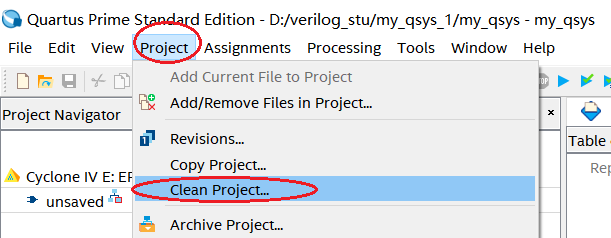

(8)clean project(如果编译到一半,突然电脑关机了等类似的问题,再次编译出现一些奇怪的错误,该功能可能帮你解决问题)

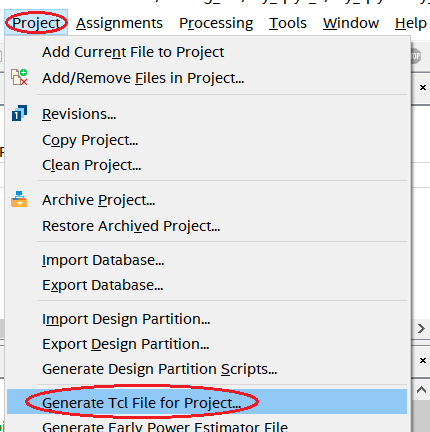

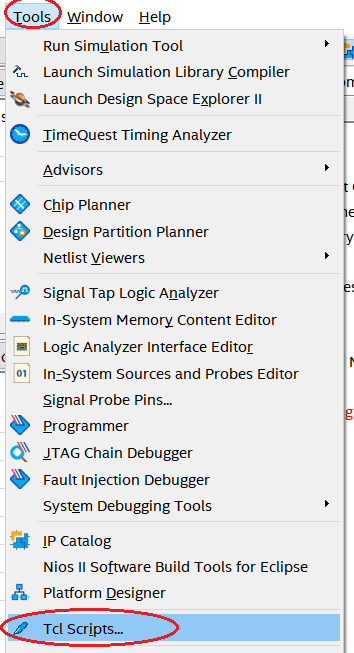

(9)产生/使用tcl管脚配置文件(快速配置管脚,建议新工程的顶层信号定义和旧工程相同)

产生TCL管脚配置:

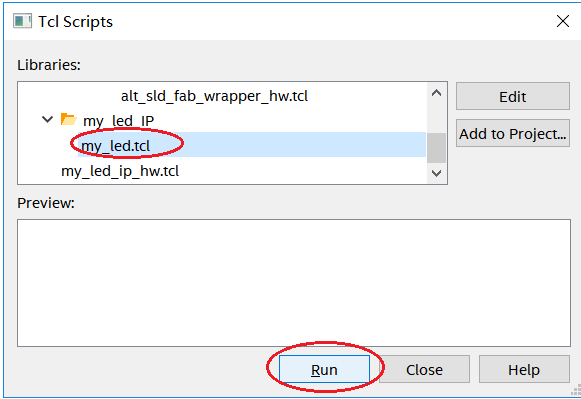

使用TCL配置管脚:

(10)工程版本整理

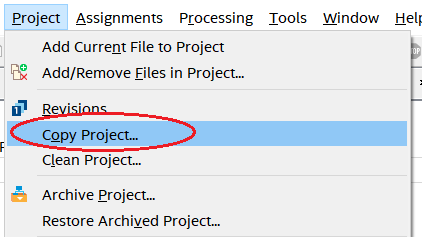

1)copy 工程,之后自己选择目录然后确定即可。

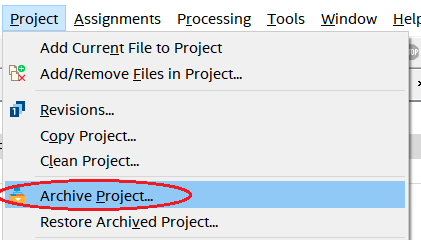

2)打包工程(可生成.qar文件,然后发给别人,别人可直接用quartus打开)

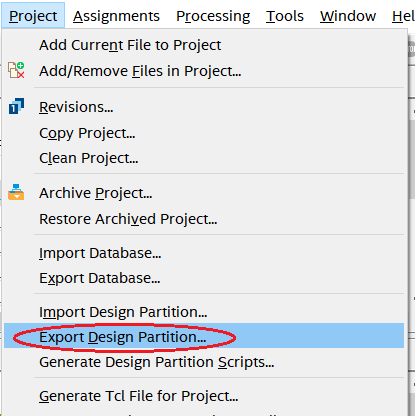

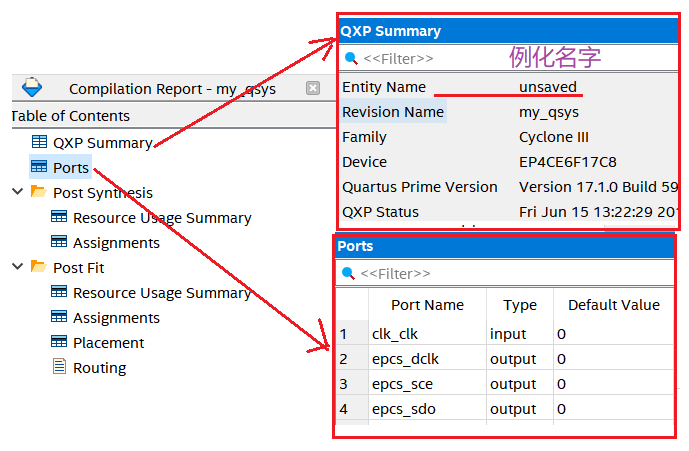

3)生成.qxp(网表,比如自定义IP核,自己写的程序不想给别人看,这里要注意的要是用signal tap观察的话,需要把这些信号例化后在观察,否则观察不到信号的)文件给别人使用

第一步:

第二步:之后在其他工程中点击 file -> open 选择xx.qxp,会看到如下信息,然后可以去例化该模块或设置为顶层直接使用。

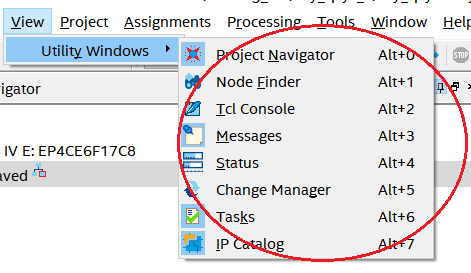

(11)主界面窗口调整(不小心把某些窗口关掉了,怎么找回来)

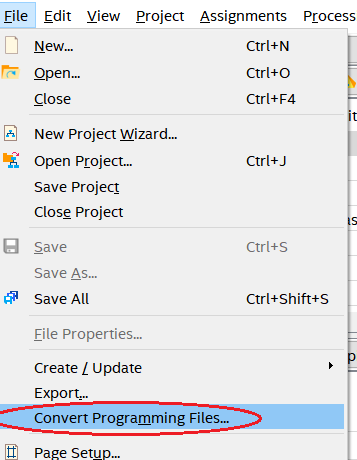

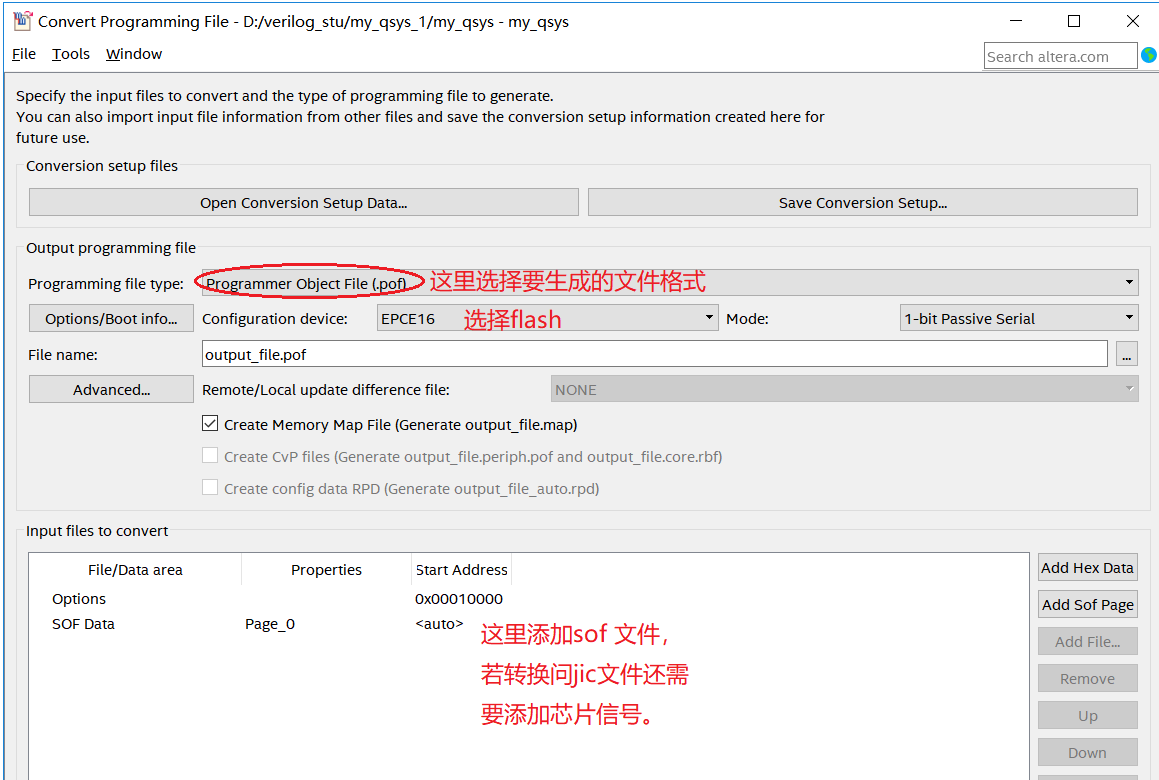

(12)转换固化文件(最终固化到器件的flash中)

第一步:

第二步:

(13)手动加入IP核(有时候生成IP后,由于某种原因IP核并没有加入到工程中,那怎么办呢)

加入xx.qip的文件即可,IP核的其他xx.v文件都不用加。

(14)signal tap 观察信号时,某些被优化怎么办?

把中间信号改为该模块的output类型,然后重新编译一遍吗,再次加入该信号即可。

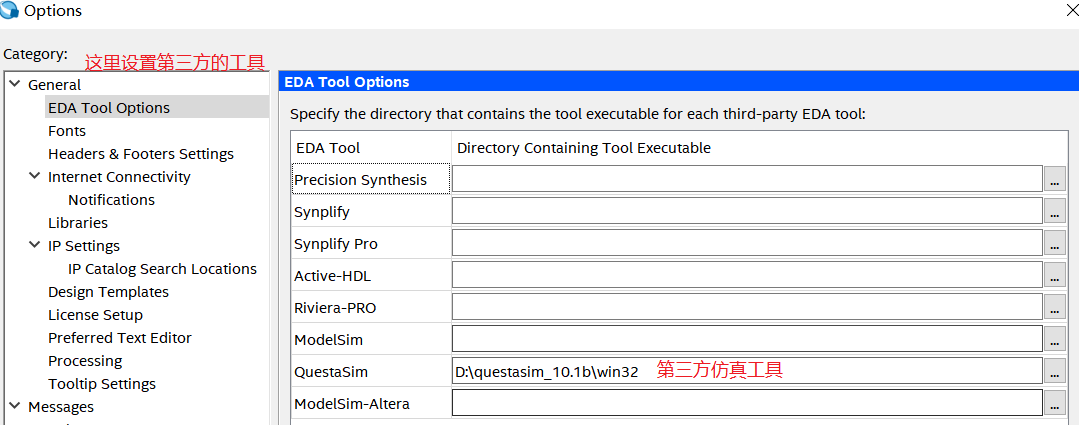

(15)设置第三方仿真或者综合等工具

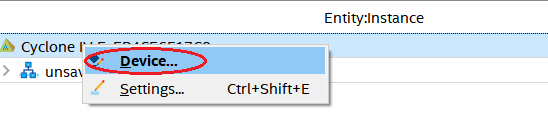

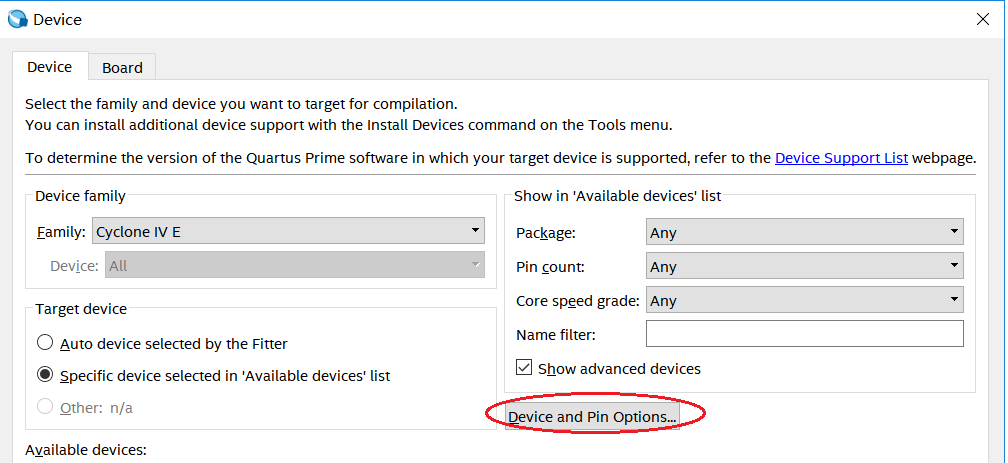

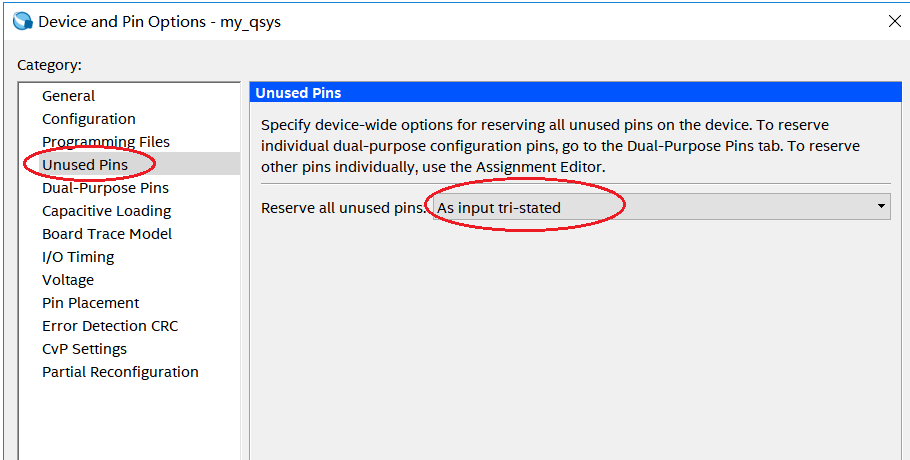

(16)没有用的管脚设置

第一步:

第二步:

第三步:

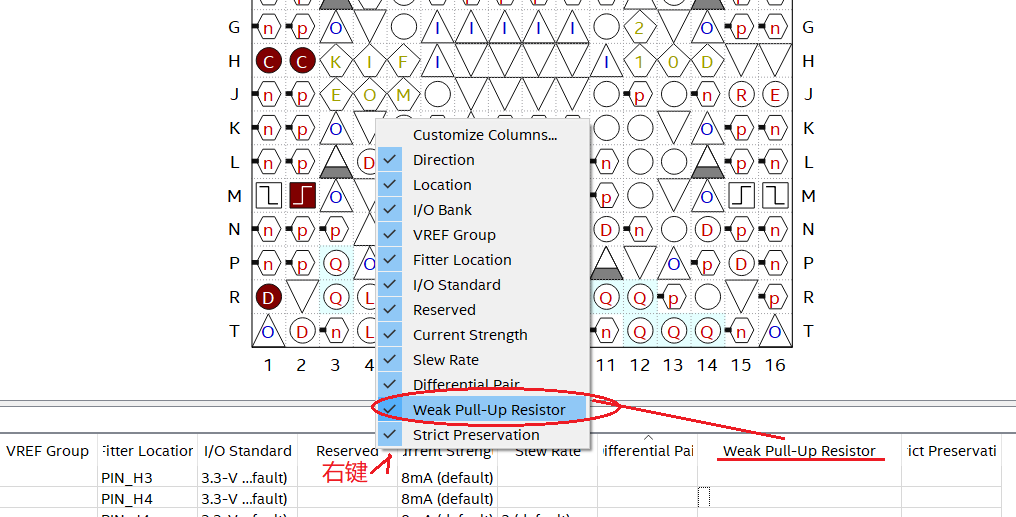

(16)设置管脚上拉[比如IIC需要等]

打开Pin Planer,然后如下图所示:

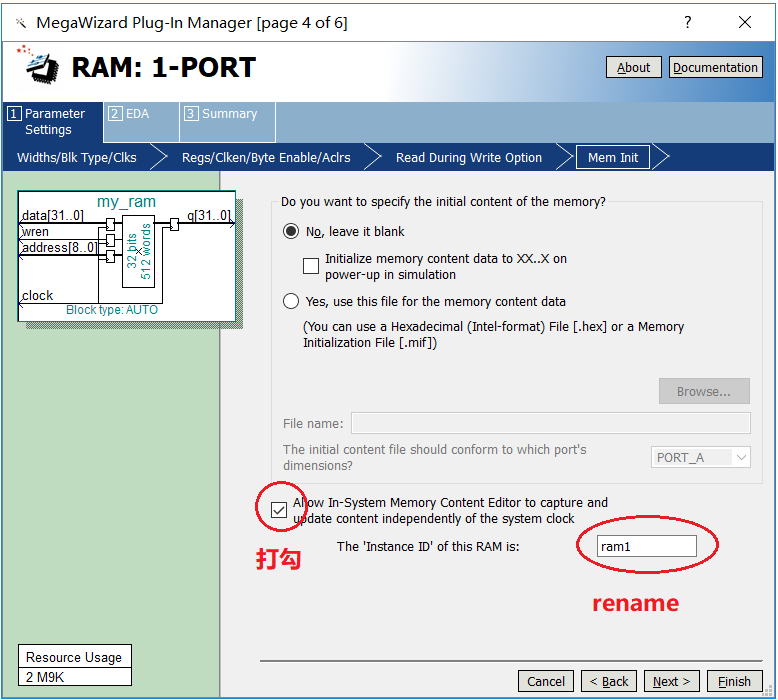

(17)通过usb-baster 查看ram中的数据

首先在生成ram的时候需要做一些设置,如下:

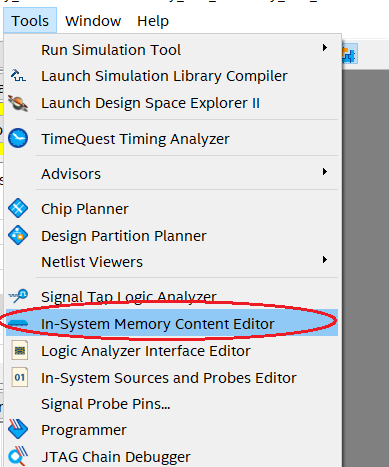

然后在下载xx.sof后,点击这里:

最后呢,我们可以看到ram中的数据如下所示: