在我上一篇博客里,我们达成一个观点,就是使用DMA(直接内存访问)的好处很明显,我之前在“Adam Taylor MicroZed系列之21”也提到使用AXI接口的DMA的好处。

虽然达成这样一个观点,但我们还有一个值得思考的问题,DMA到底是什么?

最基本的,一旦处理器配置好传输方式之后,DMA可以自己完成内存数据的搬进或者搬出,而不需要处理器的介入。如果使用方法得当,DMA可以显著地提高系统性能。

在讨论Zynq DMA的设计细节之前,让我们先要解释几个DMA控制器的原则:

典型的DMA控制器可以工作在以下三种模式:

1、 突发模式-以一个连续的操作方式来传输一个完整的数据包,在许多应用中,DMA的突发模式传输会拒绝处理器的总线访问,对于不同的系统而言,这有利有弊(可以是件好事,也可能是一件非常糟糕的事情。)

2、 周期挪用模式-跟处理器一起交替完成单独的DMA字节或者字传输的总线访问,这种模式可以防止处理器无法访问总线。

3、 透明模式-效率最高的传输模式,只有在处理器在执行任务而不需要访问外部系统总线的时候,DMA才能传输数据。

DMA控制器支持scatter/gather操作,这是一个非常有用的特性,这个特性允许多个数据源的数据传输到同一个目的地址,或者同一个源地址的数据传输到不同的目的地址(也可以称为“buffers”)

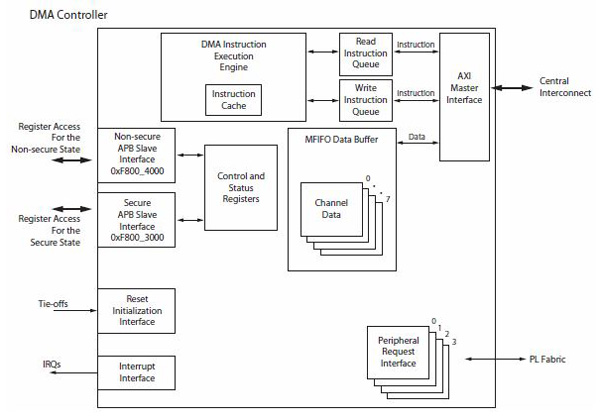

Zyng SoC是基于ARM内核的处理系统,它有一个DMA控制器,该DMA控制器连接在Zynq的AXI4中央互连架构上,通过AXI总线来传输数据,它在系统 存储器和Zynq的可编程逻辑单元(PL)之间完成64位的AXI总线传输。如下图所示,Zynq DMA有8个通道,可以同时执行8个DMA传输操作。

尽管Zynq DMA可以在系统存储器到PL(包括PL中的Zynq外设)之间发起双向传输,但是它不支持在Zynq PS的外设之间发起传输,因为,这些外设没有支持DMA操作的流控制信号。然而,在Zynq SoC中,有一些IO外设,它们自身有DMA控制器,可以支持IOP和系统存储器之间的高速数据传输。这些外设包括:

1、 以太网控制器

2、 SDIO控制器

3、 USB控制器

4、 器件配置控制器

如果器件采用了ARM TrustZone技术,Zynq SoC也可以支持安全寄存器访问。

赛灵思则提供了一个简单有用的驱动文件(xdmaps.h),这个文件可以用在BSP中来配置和初始化DMA传输。在我的下一篇博客中,会讲到如何用这个文件来实现一个简单的DMA传输。

原文链接:

http://forums.xilinx.com/t5/Xcell-Daily-Blog/The-Zynq-PS-PL-Part-Eight-Z...