使用Vivado的block design

(1)调用ZYNQ7 Processing System

(2)配置ZYNQ7系统

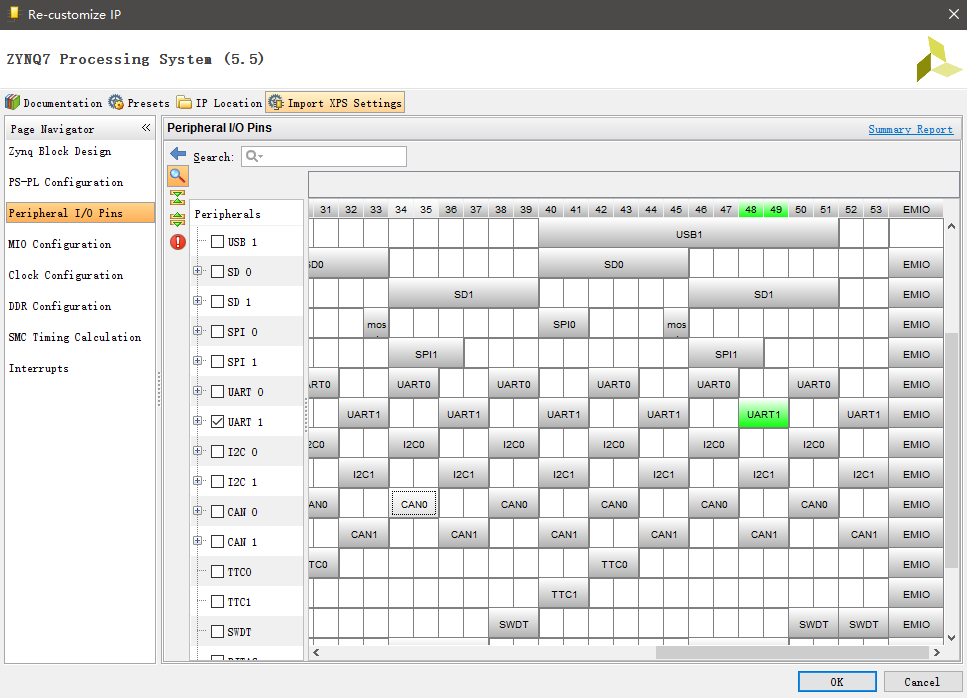

(3)外设端口配置

根据开发板原理图MIO48和MIO49配置成了串口通信。

(4)串口波特率的配置

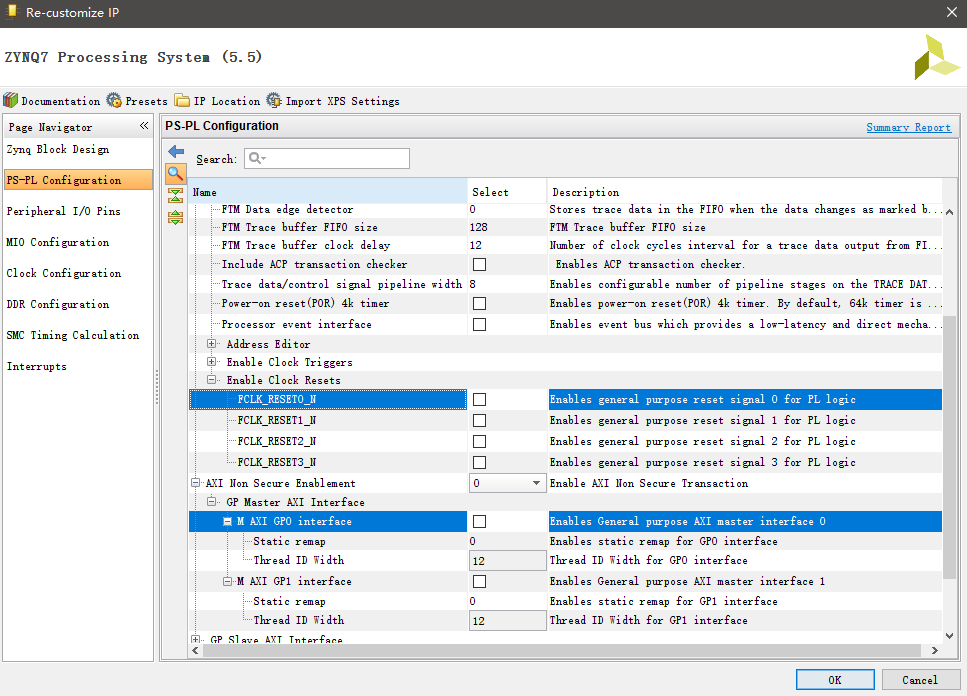

(5)关于AXI总线的配置

(6)时钟配置界面

这里可以配置ZYNQ系统输入时钟,CPU的工作时钟,DDR工作时钟,还有其他外设的工作时钟。

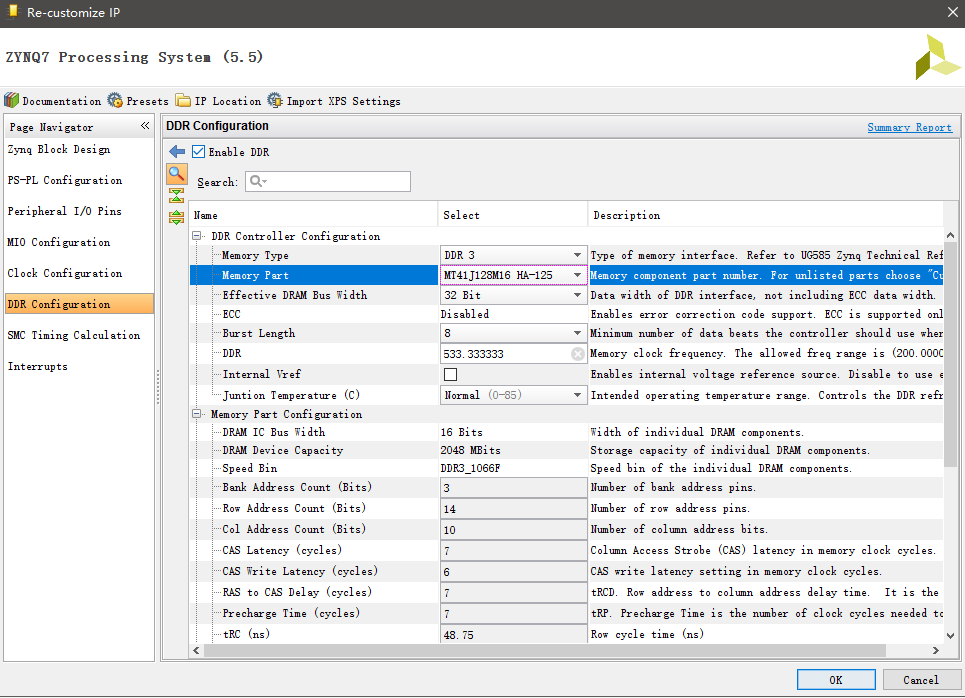

(7)DDR的配置

重点在于选择DDR的信号,其他参数会自适应。

(8)Run Block Automation完成对ZYNQ7 Processing System IP核的配置

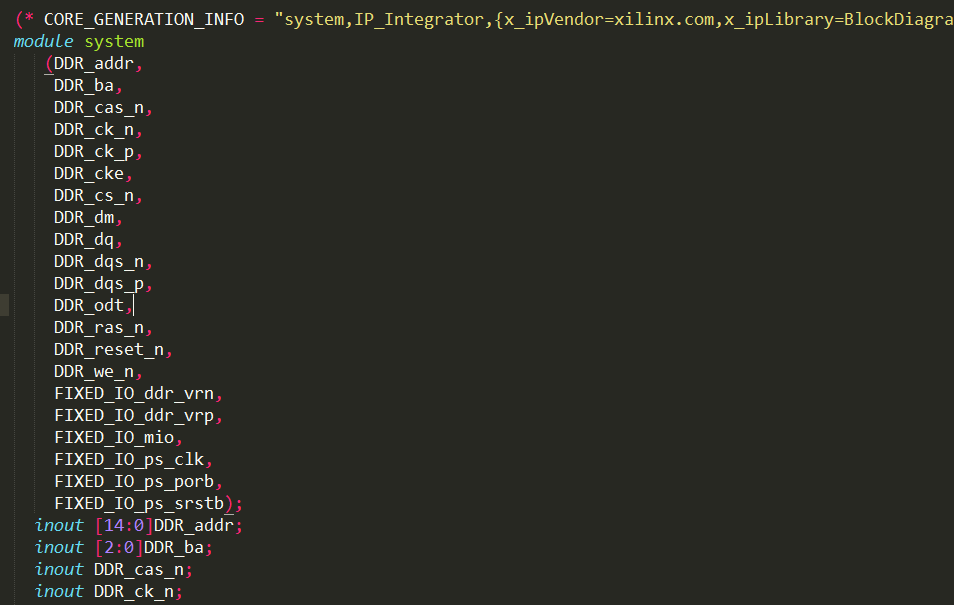

运行完Run Block Automation之后,会生成ZYNQ系统外部管脚,如下图:一个是DDR接口,一个是FIXED_IO接口。

(9)Generate Output Products

此步骤是用来生成Diagram Block Design的HDL源文件以及相应端口的约束文件。

生成的system.v文件内容如下图所示,其实就是这个block design的顶层文件:

(10)生成整个工程的顶层文件

生成结果为:

注意:如果系统只使用了PS部分的资源,没有使用PL部分的资源,则不需要再vivado下编译和生成bit文件了。

(11)硬件导入SDK

File ->Export->Export Hardware..

(12)启动SDK开发环境

File->Launch SDK

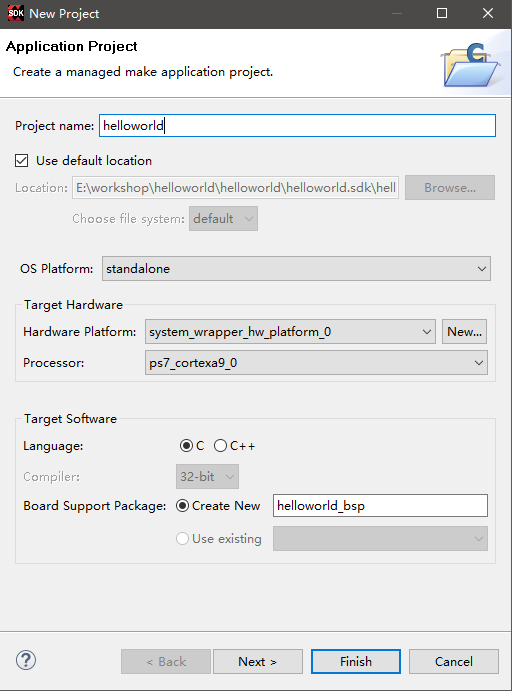

(13)SDK软件编程

File->New->Application Project,即新建一个SDK的软件工程。

选择工程模板Hello World

新建的Hello World工程

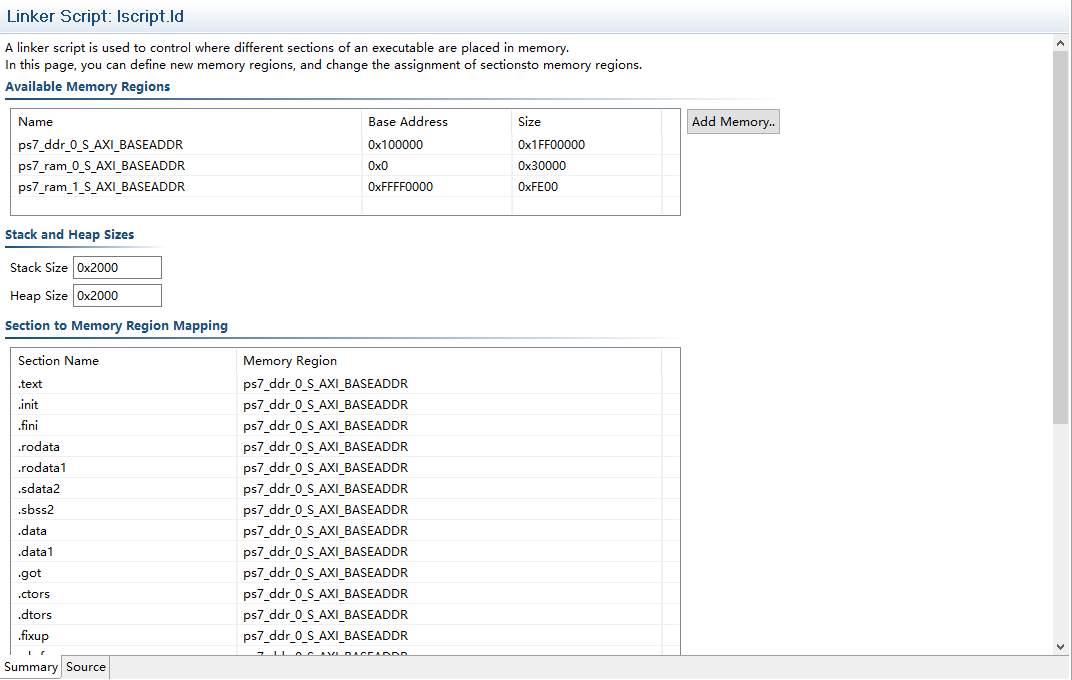

其中工程里面的lscript.ld文件是用来定义程序或者数据是在内部的RAM还是外部的DDR里面。

(14)编译软件程序

Build Project