我要做CPU_4

1.下面来分析数据在不同时钟域之间同步的问题

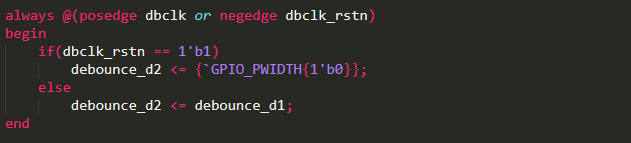

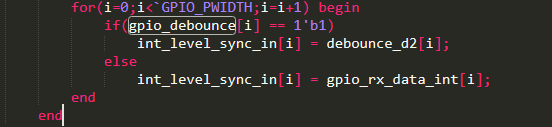

dbclk时钟域的debounce_d2寄存器(多bit)

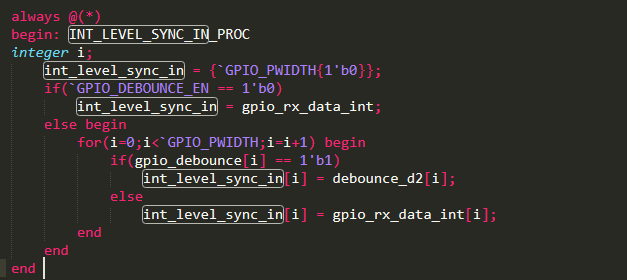

经过组合逻辑,变为int_level_sync_in

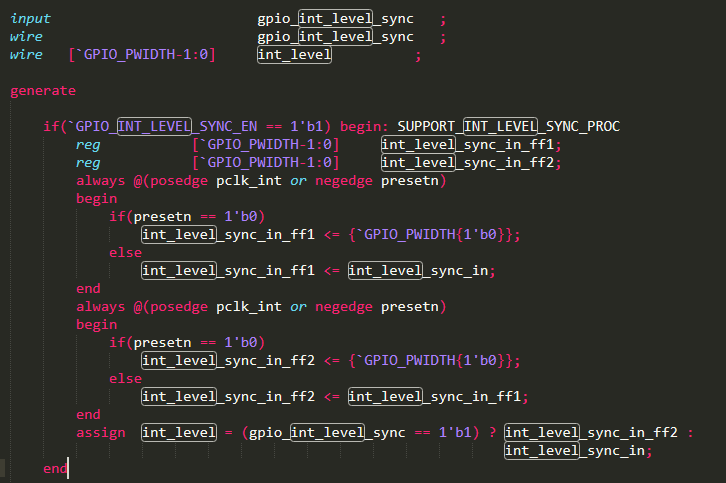

进入pclk_int时钟域进行同步

Int_level_sync_in本身就是组合逻辑,同步到pclk_int时钟域本来就只需要打两拍就够了。

不进行时钟同步:

此处有一个疑问,本人也不是很理解,也从未见过?

就是这个debounce_d2是多比特的寄存器 ,在dbclk时钟域,然后通过组合逻辑转成了int_level_sync_in(reg)。但这个int_level_sync_in 寄存器直接用pclk_int 时钟打了两拍到了pclk_int这个时钟域。多比特的寄存器跨时钟域还能这么搞吗?也许这其中的玄机在输入信号debounce操作。

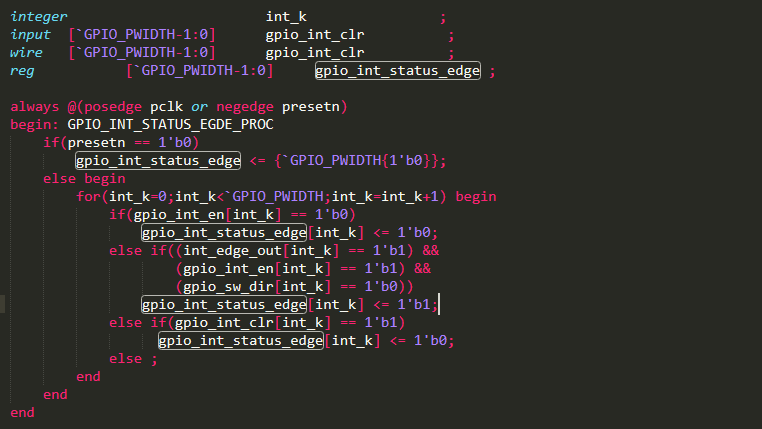

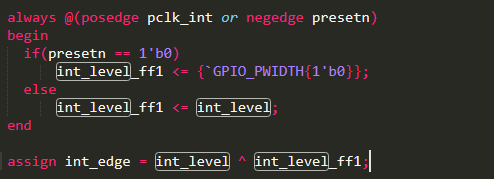

将得到的int_level信号再用时钟pclk_int打一拍,然后按位进行异或运算,可以检测出int_level信号的边沿。

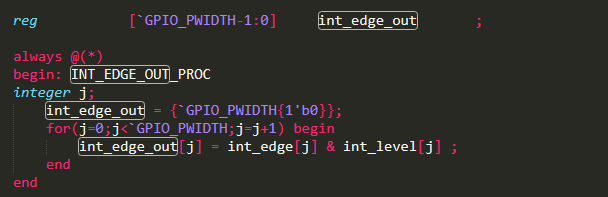

此处是输出在int_level跳转出的int_level值。心得体会:想要截取某一信号的哪一部分,首先分析这个信号的规律,然后做出相应的控制逻辑使能信号,最后在做我们想要的输出信号。

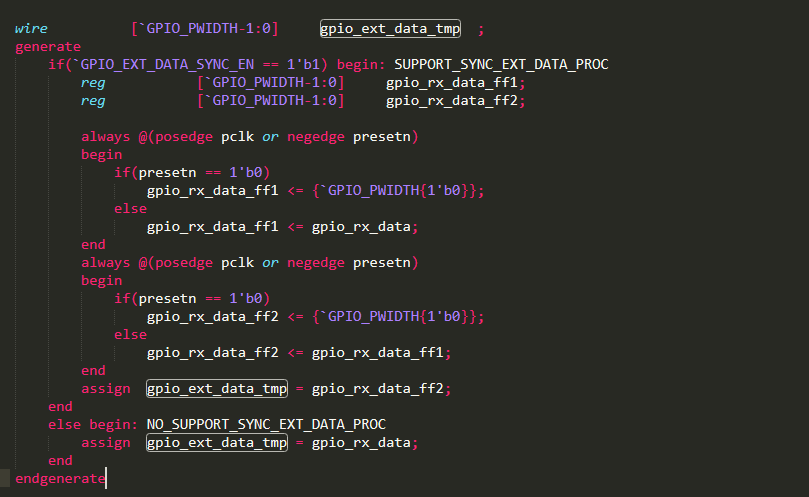

2. gpio_rx_data又一个数据流处理路径

当GPIO_EXT_DATA_SYNC_EN宏定义使能时,gpio_rx_data数据在pclk时钟域打两拍,然后与gpio_ext_data_tmp相连,如果宏定义没有被使能,则直接与之相连。

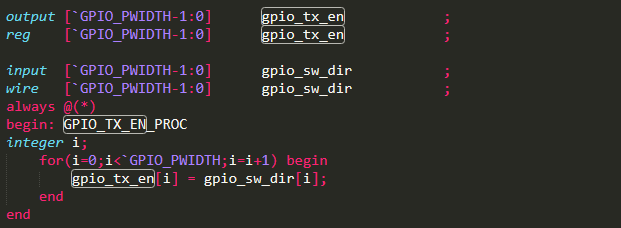

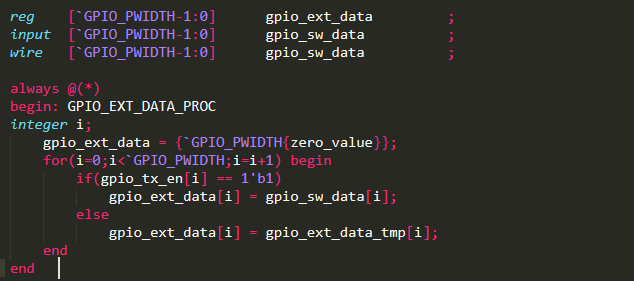

数据发送使能

输入信号的环出操作

使用发送使能信号对gpio_ext_data进行输出控制

这里其实就是一个数据的环出操作。

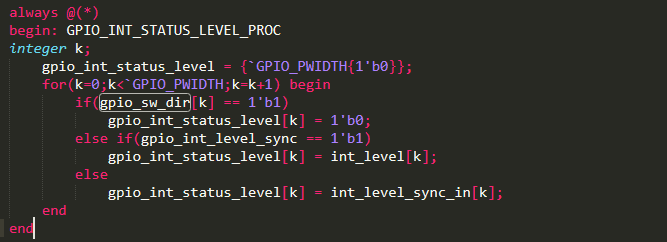

gpio_int_status_level选择,这里并不知道为什么是这么个逻辑,首先需要进一步弄清楚外部输入控制信号是什么意思,gpio_sw_dir.

不晓得要检测这个边沿搞什么用。