在Vivado下在线调试是利用ILA进行的,Xilinx官方给出了一个视频,演示了如何使用Vivado的debug cores,下面我根据这个官方视频的截图的来演示一下:

官方的视频使用的软件版本为2012.2,不过在2015.3下也是差不多的。

第一步:标记需要debug的信号

例如:

VHDL:attribute mark_debug of sineSel : signal is "true";

attribute mark_debug of sine : signal is "true";

Verilog: 在需要debug的信号前加上 (* MARK_DEBUG = "TRUE" *) 或者(* mark_debug = "true" *)

第二步:设置debug

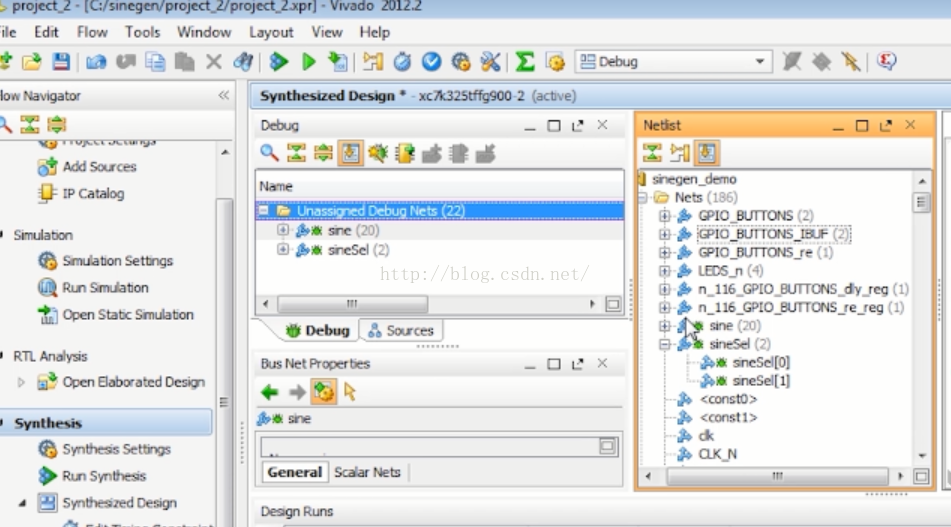

首先打开synthesis design,可以看到之前标记的debug信号,然后点击tools,选择set up debug

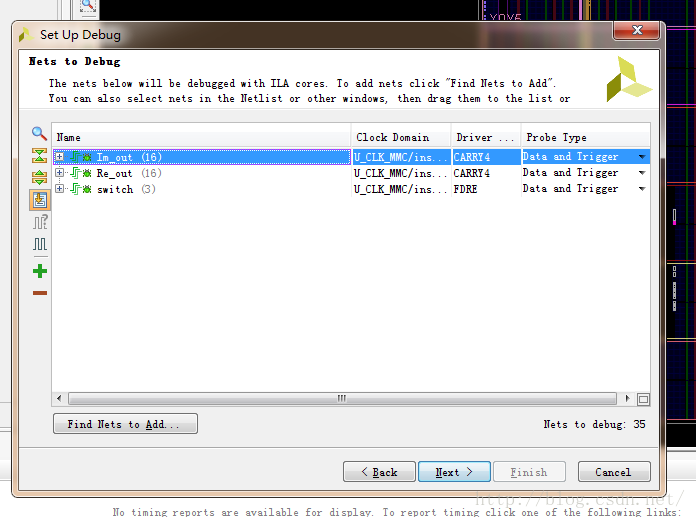

点击find nets to add,可以找到之前标记的信号,把信号添加完毕,检查Clock Domain是否正确,点击下一步。

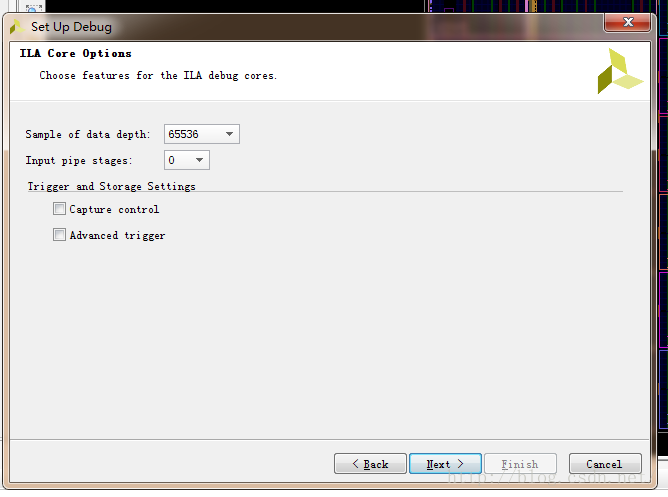

在下图中,将Capture control和Advanced trigger打上勾,这样在后面的调试中可以使用高级的捕获功能,再下一步,这样ILA的设置工作就完成了。

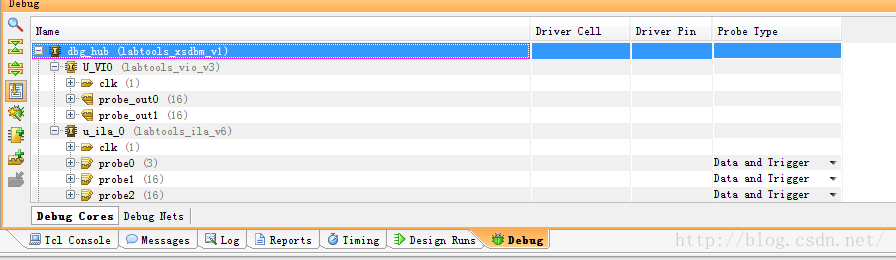

可以在debug视图中看到,Vivado自动帮我们插入了dbg_bug和ila,接下来生成bit文件,写入FPGA中,在Vivado的调试界面上就能进行在线的波形输出了。

转载:https://blog.csdn.net/u013564276/article/details/49663599