1、实现原理

SignalTap II获取实时数据的原理是在工程中引入Megafunction中的ELA(Embedded Logic Analyzer),以预先设定的时钟采样实时数据,并存储于FPGA片上ram资源中,然后通过JTAG传送回Quartus II分析。可见SignalTap II,其实也是在工程额外加入了模块来采集信号,所以使用SignalTap II需要一定的代价,首先是ELA,其次是ram,如果, 工程中剩余的ram资源比较充足,则SignalTap II 一次可以采集较多的数据,相应的如果FPGA资源已被工程耗尽则无法使用SignalTap II调试。

2、创建STP文件

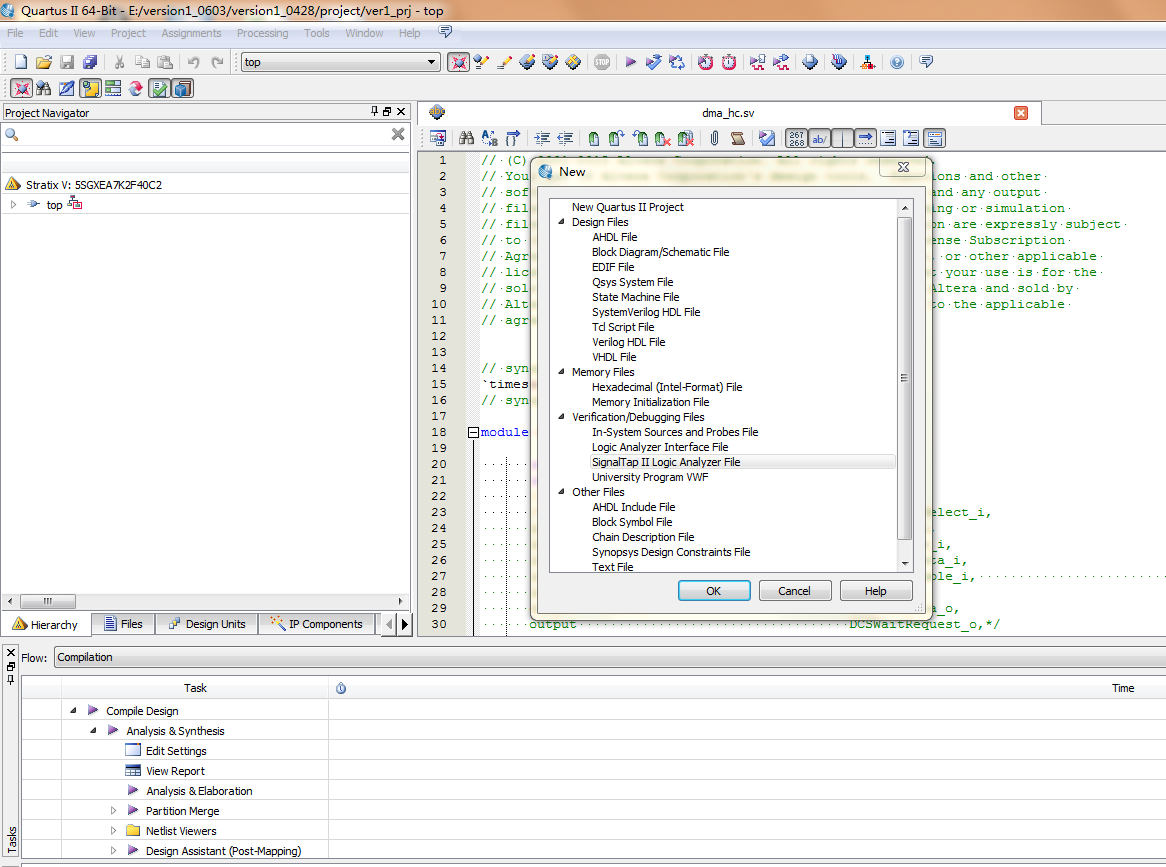

在quartus界面中点击file,选中new,弹出下面框:

选中SignalTap II Logic A nalyzer File点击OK,弹出下面框:

3、在STP文件中添加实例(instance)

添加方法:在上图中的instance窗口中点击右键,选择create instance。

默认情况下,STP中有一个默认名为auto_signaltap_0的instance,双击auto_signaltap_0可以修改为自己定义的名字

4、在instance中添加观测节点(nodes)

点击Edit,选中Add Nodes...(此处有一个需要注意的:上面的步骤必须在打开一个工程后操作,否则Edit中的Add Nodes...将会是灰色,无法选中) ,然后弹出:

这个时候就需要添加你所需要抓取的信号。Look in中选择抓取的信号所在的模块,Filter修改为:

SignalTap II:pre-synthesis,在Named中输入所需抓取的信号名,点击List,在Nodes Found中就会出现该信号,双击该信号,该信号就会出现在Selected Nodes里面。同样在Named中输入另外需要抓取的信号,使之出现在Selected Nodes里面。添加完所有的信号后,点击OK。

5、为instance添加采样时钟

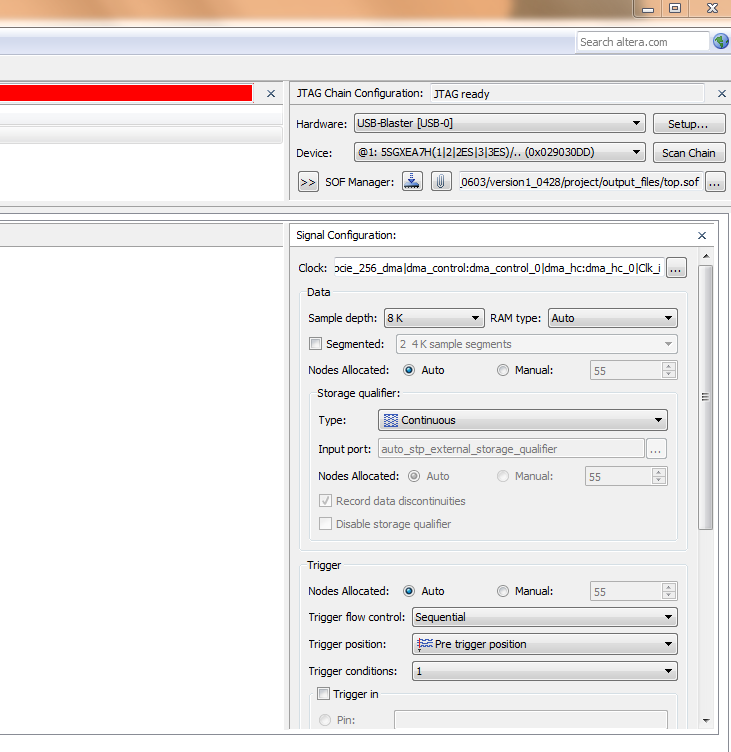

点击软件中下部的Setup按键,在右边会出现:

点击上图的clk旁边的[...]将会弹出与上面一样的Noder Finder窗口,选择好合适的时钟信号。然后设置一些基本的参数:

采样深度,Sample depth 个人建议选大些,但是又不能超过FPGA资源,不然在后面的编译会报错。

RAM类型,这个默认为auto,不用管

触发,Trigger 这个在初期使用signal tap就选择默认,后期可以根据具体信号波形来设置。

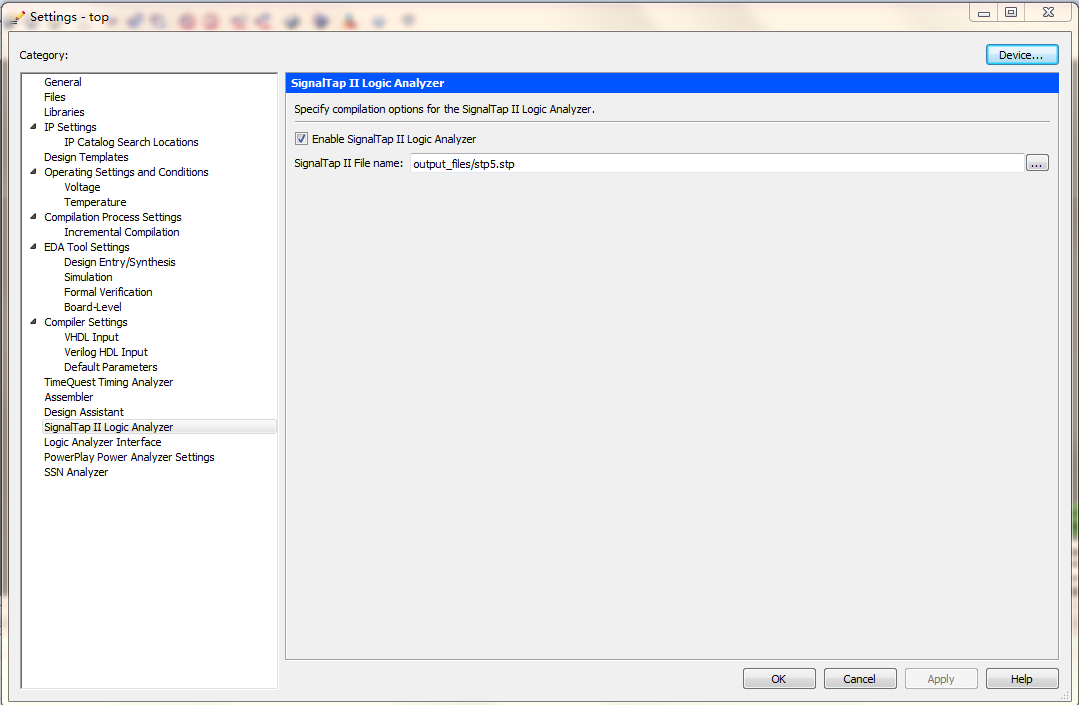

6、重新编译添加了signal tap工程

在quartus10.1中一般在上面的步骤都做好后,关闭signal tap窗口一直点击OK就行。为了确保工程中的确添加了我们刚刚新建的stp文件,可以打开工程,选中Entity中的顶层,右键点击settings,就会出现:

7、编译和下载代码

按照一般的方法,编译和生成sof文件。下载代码需要在SignalTap II 中下载,双击stp文件,就会弹出:

点击右上角的SOF Manager后面的[...],选择好刚刚生成的SOF文件,然后点击program device。

8、抓取数据,观测波形

在下载好sof后,点击Instance Manager旁边的run analyzer(也就是红色的三角标志),就可以观察波行了。

转载自:http://www.eefocus.com/zh880813/blog/16-06/385441_3c219.html