在所从事的项目中需要用到PCIE和DMA,经过再三研究,反复查看相关资料,终于弄懂了**alon_MM DMA Interface for PCIe的使用方法。

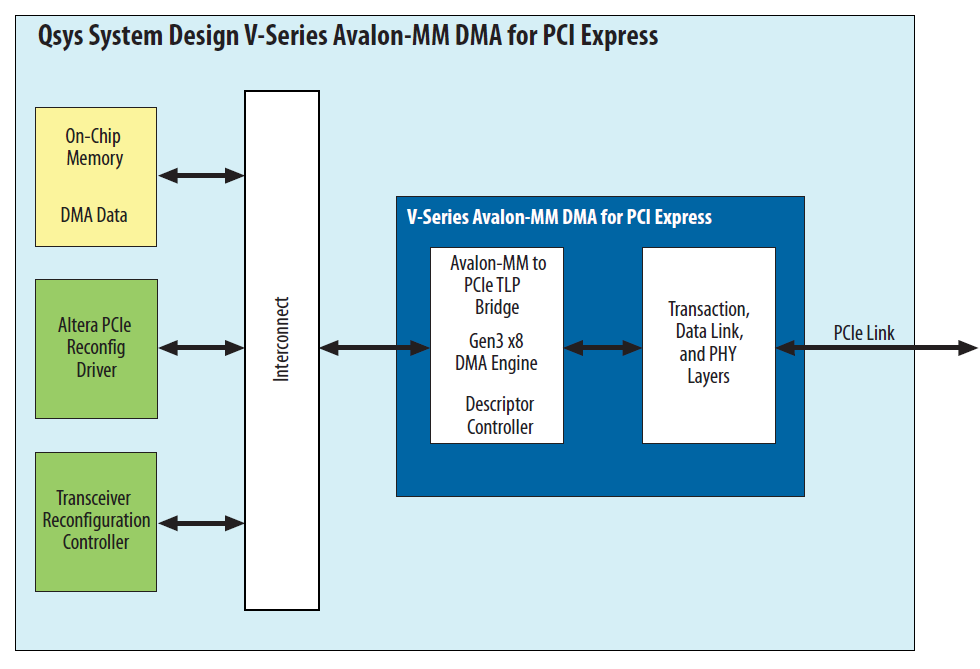

PCIE在fpga和上位机之间起着中间桥梁的作用,具有双向传输数据的功能。以下是**alon_MM DMA Interface for PCIe结构图,后面再分别详细介绍。

该ip可以使用Internal Descriptor Controller和External Descriptor Controller,下文所做介绍以Internal Descriptor Controller为基础。

接口介绍:

Read DMA **alon-MM Master Port:主要完成两方面的工作:1、该模块发送读请求从host memory中取descriptor table,并将descriptor table通过**alon-MM Master 写入Descriptor Controller FIFO

2、从source address读取诗句之后,将数据写入**alon-MM 地址映射的外部DDR中。

Write DMA **alon-MM Master Port:该模块向**alon-MM 地址映射的外部DDR发送读请求,将读取的数据写入系统内存中。

RX Master Module:将从pcie接收到的读和写信号发送给**alon-MM ,request给连接在internnect的component.当Descriptor Controller在内部建立时,BAR0在内部使用,不能用作外部使用。上位机通过RXM给Descriptor Controller的寄存器进行编程,包括descriptor table的地址和大小。

descriptor controller 指示Read Data Mover 取descriptor table,并存在fifo中,controller取table并指导DMA在**alon-MM 和 PCIe之间传输数据。

TX Sl**e Module:将**alon-MM Master的读和写请求发送给PCI Express TLPs;当DMA完成时,descriptor controller利用此接口向上位机中的descriptor data写DMA status,并发送MSIinterrupts.

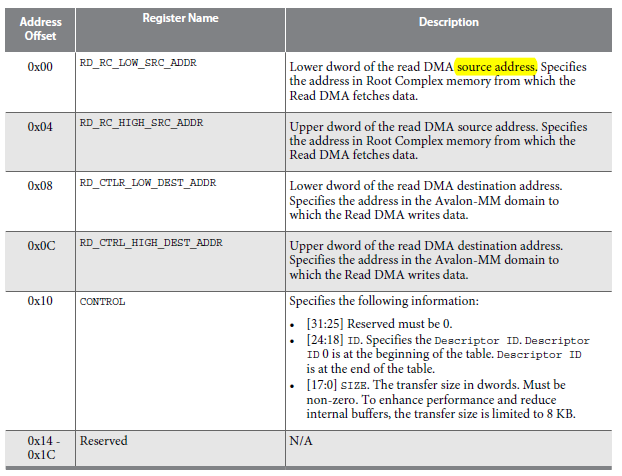

DMA Descriptor Controller Registers

上位机通过bar0来配置DMA Descriptor Controller Registers,read controller的地址偏置为0x0000,write controller的地址偏置为0x1000

DMA Descriptor Controller Registers for Read DMAs

RD_RC_LOW_SRC_ADDR = 0x0000 (The base address for the read descriptor table in the Root Port

RD_RC_HIGH_SRC_ADDR = 0x0004

WR_TABLE_SIZE=0x0014

该寄存器表示一共有多少个descriptor table

WR_CONTROL =0x0018

该寄存器[0]表示done ,当dma完成时,向descriptor table中的status写done bit。

DMA Descriptor Controller Registers for Write DMAs

0x00,0x04:源地址

0x08,0x0c:目的地址

0x10:[24:18],对应descriptor的ID号,[17:0],DMA发送的数据量。

完成一次DMA操作的步骤

1、计算需要分配的内存大小:描述一个descriptor 的status需要的内存为32bit,即4bytes,描述一个descriptor table需要的内存32bytes。一共最多有128个descriptor,存放status需要的内存为512bytes,存放descriptor table 需要32bytes*128 (针对 read DMA,write DMA同样),分配内存起始地址base_address。

2、给存放数据分配内存,

3、descriptor table存在descriptor status之后,存放第一个descriptor table的起始地址为base_address+0x200

4、创建descriptor table,按照Descriptor Table Format的格式

5、通过编程配置DMA Descriptor Controller register,配置status and descriptor table地址的寄存器,0x0,0x4

6、配置存放status and descriptor table的on_chip fifo address,对应的是**alon-MM address,internal on-chip FIFO是Descriptor Controller的一部分,就是RX Master看到的大小。

7、编程配置RD_DMA_LAST_PTR register,用来触发DMA。

如果只需要得到所有的descriptor 都完成后得到done的信号,只需要写最后一个descriptor id给0x10;

如果每一个descriptor完成后都返回done,需要对每一个descriptor都配置0x10。

8、软件可以监测到done信号。

转载自:http://www.eefocus.com/zh880813/blog/16-06/385376_89d9c.html