2018-2019-1 20165333 《信息安全系统设计基础》第5周学习总结

教材内容总结

1.存储技术

(1) 随机访问存储器分为:静态随机访问存储器和动态随机访问存储器,即SRAM,DREM。

SRAM:将位存储在一个双稳态的存储器单位里。

DRAM:将位存储为对一个电容的充电。

- 应用

SRAM应用在高速缓存存储器,DRAM应用在主存帧缓冲区。

DRAM被分为d个超单元,一个超单元等于W个DRAM单元,所以DRAM存储d*w位信息

- 增强的DRAM

- 非易失性存储器

非易失性存储器有:电子可擦除PROM,可擦可编程ROM,闪存

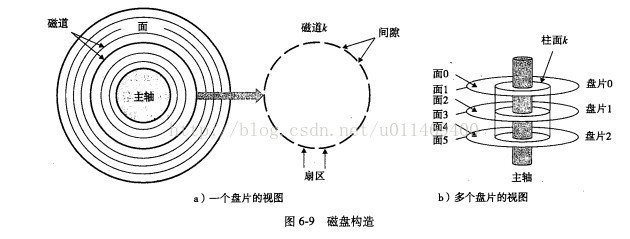

(2)磁盘存储

- 磁盘构造:

公式:磁盘容量=字节数 * 平均扇区数 * 磁道数 * 表面数 * 盘片数。

对扇区的访问时间包括:寻道时间,旋转时间,传送时间。

- 逻辑磁盘块

磁盘中有一个固件设备--磁盘控制器(盘面、磁道、扇区)

-

固态硬盘SSD

-

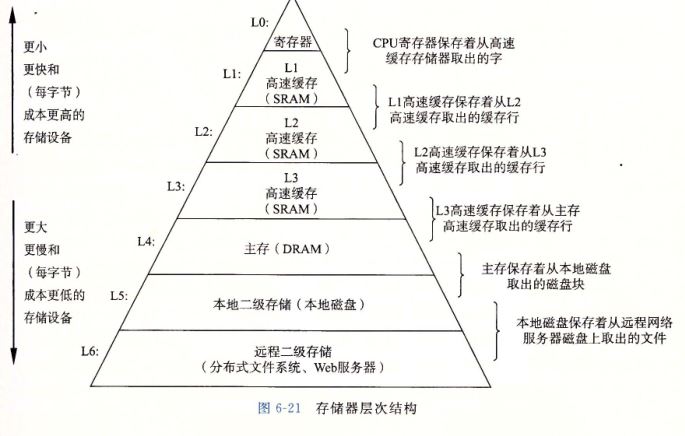

存储器层次结构示意图

局部性

- 原理:引用最近引用过的数据项

(1) 时间局部性:被引用过一次的存储器位置很可能在不远的将来再被多次引用。

(2)空间局部性:被引用过一次的存储器位置附近的数据可能在不远的将来被引用。

(3)取指令的局部性:指令也是存储在存储器中的,循环的时间和空间局部性是好的。循环体越小,迭代次数越多,局部性越好。

高速缓存存储器

- 通用的高速缓存存储器结构

一个计算机系统每个存储地址有m位,形成M=2^m个不同的地址。

高速缓存被组织成一个有S=2^s个高速缓存组的数组,每个组包含E个高速缓存行,每个行是由- 一个B=2^b字节的数据块、一位有效位以及t=m-(b+s)个标记位组成,唯一标识存储在这个高速缓存行中的块。

高速缓存的结构用元组(S,E,B,m)来描述,高速缓存的大小C = S * E * B。

直接映射高速缓存

-直接映射高速缓存:每个组只有一行的高速缓存。

组选择:

高速缓存从w的地址中间抽取出s个组索引位

组索引位:一个对应于一个组号的无符号整数。

行匹配:

判断缓存命中的两个充分必要条件:该行设置了有效位;高速缓存行中的标记和w的地址中的标记相匹配

字选择:确定所需要的字在块中是从哪里开始的。

- 组相联高速缓存

组相连高速缓存中的组选择:与直接映射高速缓存中的组选择一样,组索引位标识组。

组相连高速缓存中的行匹配和字选择:把每个组看做一个小的相关联存储器,是一个(key,value)对的数组,

以key为输入,返回对应数组中的value值。高速缓存必须搜索组中的每一行,寻找有效的行其标记与地址中的相匹配。

组相连高速缓存中不命中时的行替换:最简单的替换策略是随机选择要替换的行,其他复杂的策略则使用了局部性原理,例如最不常使用、最近最少使用等。

- 全相联高速缓存

全相连高速缓存中的组选择:只有一个组,没有组索引位。

全相连高速缓存中的行匹配和字选择:与组相连高速缓存是一样的,但规模大很多,因此只适合做小的高速缓存,例如虚拟存储系统中的翻译备用缓冲器。

- 有关写的问题

直写:

立即将w的高速缓存块写回到紧接着的第一层中

缺点是每次写都会引起总线流量。

写回:

只有当替换算法要驱逐更新过的块时,才能把它写到紧接着的低一层中,由于局部性,写回能显著减少总线流量。

缺点是增加了复杂性。

另一个问题是如何处理写不命中。

写分配:加载相应的低一层中的块到高速缓存中,然后更新这个高速缓存块。 缺点是每次不命中都会导致一个块从低一层传送到高速缓存。

非写分配:避开高速缓存,直接把这个字写到低一层中。

- 高速缓存参数的性能影响

不命中率:不命中数量/引用数量

命中率:1-不命中率

命中时间:从高速缓存传送一个字到CPU所需的时间,包括组选择,行匹配,字抽取的时间。

不命中处罚:由于不命中所需要的额外时间。

综合:高速缓存对程序性能的影响

- 存储器山

一个程序从存储系统中读数据的速率称为读吞吐量,或者读带宽,通常以兆字节每秒(MB/s)为单位。

读带宽的时间和空间局部性的二维函数称为存储器山。