基于FPGA+USB2.0的图像采集系统测试小结-mt9m001

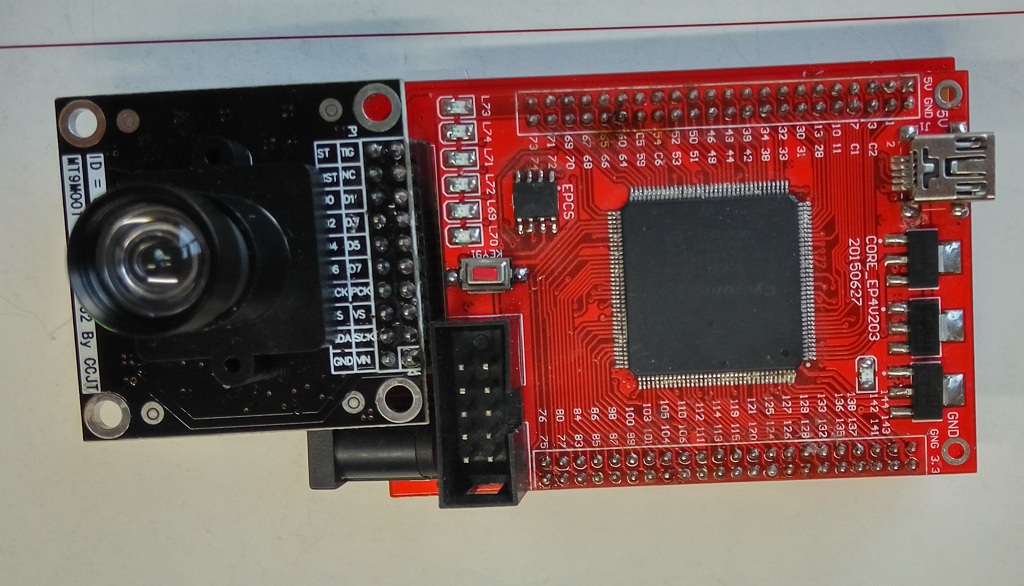

该系统采用层层惊涛出品的FPGA_VIP_USB_V102板卡测试

板卡分为:核心板、底板、摄像头板

核心板采用:ep4ce10e22(eo4ce6e22兼容)作为主控

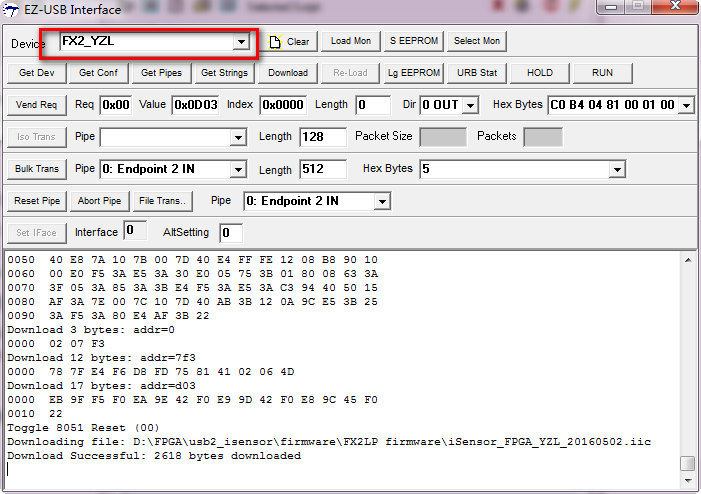

底板采用:cy7c68013A作为usb传输芯片

摄像头板(mt9m001c12stm):时钟由fpga提供,可编程提供24M、48M或12M

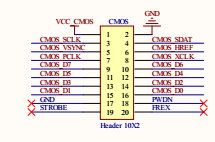

摄像头接口(标准接口,若使用非标准接口,可以按照此跳线)

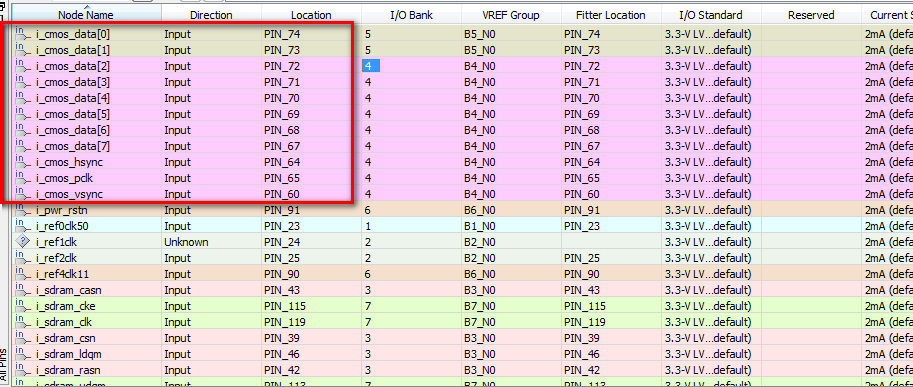

管脚分配(也可以根据实际情况,重新分配管脚定义)

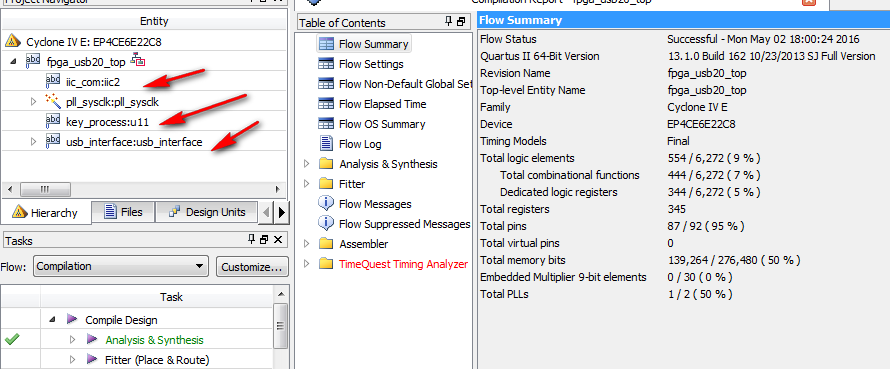

工程采用verlog编程(可以在对应模块中,修改配置文件,修改摄像头寄存器参数达到修改分辨率的目的)

1、修改xclk时钟,可以修改分帧率

/////////////////////////////////////////////////

// global assignment

assign o_cmos_xclk = sys_clk48;

2、修改寄存器参数,可以修改图像分辨率,需要和上位机对应

5 : lut_data <= {8'h03,16'd479}; //number of rows -1 : 480

6 : lut_data <= {8'h04,16'd639}; //number of columns - 1 : 640

默认下载640*480分辨率jic文件

usb固件与分辨率和帧率无关,固件默认情况下不需要任何修改

帧率测试(实测,极限帧率,为了稳定,可以适当降低帧率)

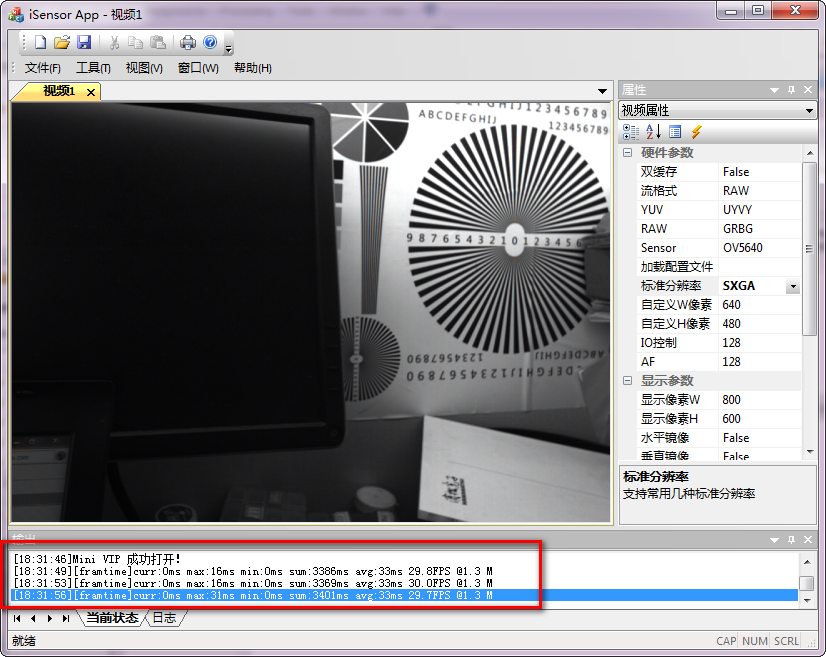

130万输出 30fps

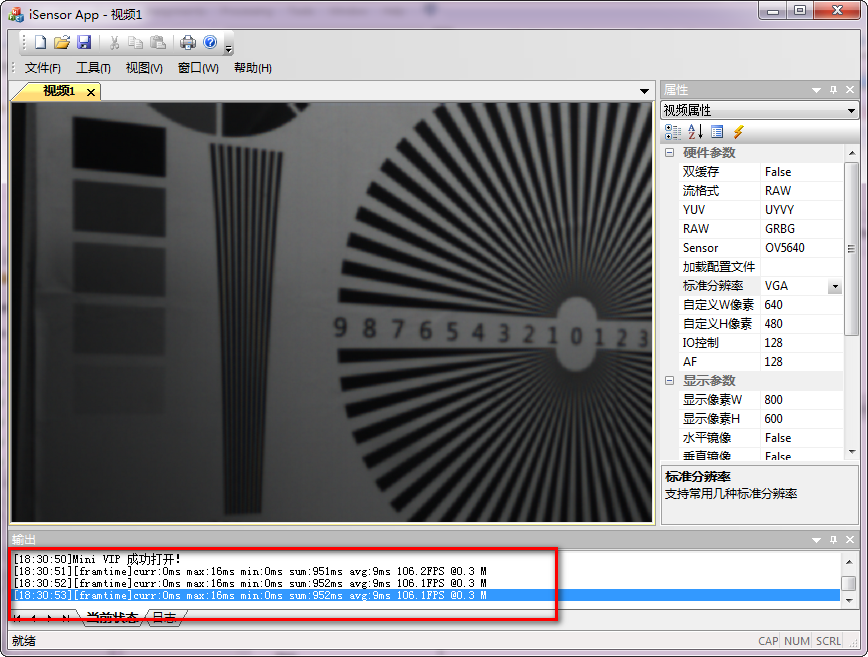

640*480输出帧率100fps