本文的话,我们首先了解一下SPI协议是什么,然后通过SPI的工作框图了解原理,然后根据代码对使用进行一下概括;

1 SPI协议

1.1 工作模式

SPI总线有四种工作模式,由CPOL和CPHA决定,模式xx = mode[CPOL:CPHA];不同模式的采样点不同;

CPOL(clock polarities时钟极性):决定SCK的起始电平是0还是1,CPOL=0表示时钟的起始电平为低;

CPHA(clock phase时钟相位): 决定数据采样点是在SCK的第1个跳变沿还是第二个跳变沿,CPHA=0表示取样点为第一个跳变沿;

就像目前遇到过的串口协议都是1bit开始位,8bit数据位,1bit停止位,无校验位;遇到的SPI协议也清一色是模式0;

1.2 数据收发

假设器件为主器件,工作在全双工模式,然后工作模式为模式0;

在SCK的上升沿时,需要MI,MO都是有效数据;所以数据应该在CS使能前或SCK采样前的下降沿准备好;(意思是数据在下降沿变化,上升沿采样)

spi的数据帧为4-32bit,数据发送以数据帧为单位,先使能片选,然后发送数据帧,然后取消片选使能;以此循坏收发数据;

1.3 注意事项

SPI协议大部分用在EEPROM和FLASH存储器上,作为板间通信协议较为常用;

SPI协议对数据的收发时序要求不高,也没有应答位;协议简单,速度较快;只要SCK和CS使能,MI,MO就可以传递数据了;

许多设备都更愿意支持模式0和模式3,因为这样的话取样的数据点都是在上升沿取样;

(上升沿通常由D触发器生成,较为稳定;下降沿的触发器触发时会有一些组合逻辑的延时,不如上升沿稳定;)

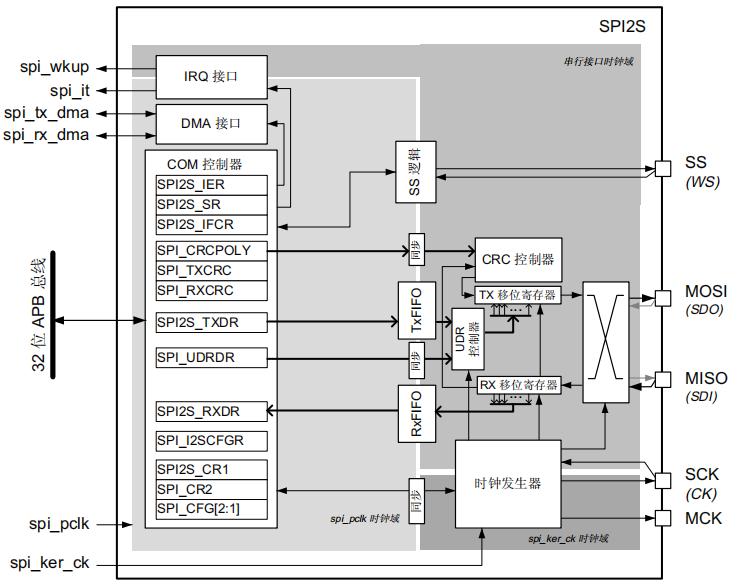

2 SPI框图

各种外设的了解无非是首先了解该外设的时钟,时钟决定传输性能;然后了解该外设的工作模式和配置原理;然后根据代码了解接口如何使用;

2.1 SPI时钟域

SPI外设的时钟域可以分为三个完全独立的时钟域,但是这些域之间的控制和状态信号需要严格同步,确保收发数据的正确;

2.1.1 spi_pclk时钟域:APB总线的工作时钟,用来访问spi寄存器时使用;

2.1.2 spi_ker_ck时钟域:主器件的SCK工作时钟,由rcc时钟生成,hal库函数中默认对其2分频后作为sck时钟;从器件的该时钟域由主器件生成;

2.1.3 串行接口时钟域:由spi_ker_ckf分频而来的时钟,用来给收发数据的移位寄存器使用;

3 hal库接口

https://www.cnblogs.com/armfly/p/12523671.html

4 W25Q128FV特性总结,随便看看

4.1 结构框图

/CS引脚:未使能前,引脚属于高阻态,芯片待机状态;片选使能,芯片电压上来,芯片自动准备收发指令数据;

/WP引脚:使能后,状态寄存器不能被修改;目的是为了防止掉电状态下的SR寄存器可能被噪音之类的修改;下面有图;

/HOLD引脚:使能CS后,如果使能HOLD,则DO为高阻态,DI,SCK信号无效;

使用spi时,可以将引脚配置为通用IO口,然后拉高,高电平不使能该引脚;

/RESET引脚:将/HOLD引脚的功能改为复位引脚,然后硬件配置复位;也可以使用复位指令软件复位;

/WP, /HOLD, /RESET引脚的功能都与QSPI的功能冲突,如果芯片配置成qspi模式,则引脚功能无效;

WEL出厂默认为0,;当WEL为1时,/WP引脚可与SR寄存器的多bit一起决定block的写保护;

w25qxx只支持spi模式的模式0和模式3,为什么呢?先占个坑;

w25qxx在SCK的上升沿读取DI的数据,在SCK的下降沿发送数据到DO;

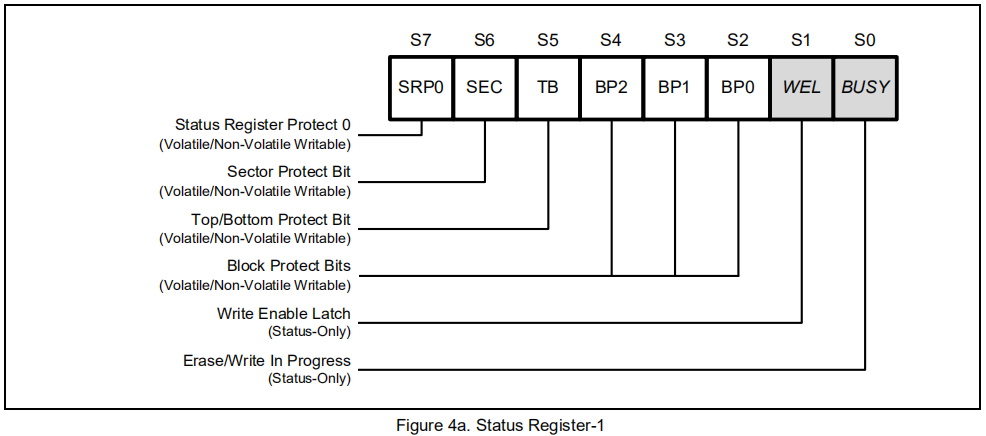

4.2 状态寄存器

w25qxx一共有3个状态寄存器;

读操作状态寄存器可以知道各种指令操作之后寄存器的状态,可以通过状态寄存器判断指令操作是否完成;

写操作状态寄存器可以配置芯片的各种功能,如写保护功能,QSPI模式,复位引脚复用等;

4.2.1 SR1和SR2:初始化值为0x00;

(S0)BUSY:当busy为1时,芯片正在执行指令,且不接收新的指令;当busy为0时,芯片不在执行指令,准备接收指令;

(S1) WEL:当wel为1时,芯片可以执行写指令;当wel为0时,不能执行写指令;上电后以及执行完各种指令后,wel会被置位为0;

(S4-S2) BP[2:0]:当配置后,对应地址的擦写操作受到保护,需要先取消保护才能修改;BP[2:0]默认初始化为0,即所有地址均可执行擦写操作;

(S5) TB:同BP[2:0]一起决定block protected;默认初始化为0;//可以通过配置SRP[1:0]和WEL来配置TB bit;

(S6) SEC:当SEC为1时,BP[2:0]的写保护单位是sector;当SEC为0时,写保护单位是block;

S[6:2]用来决定数据存储区的非易失性存储功能是否启用;如果启动,则特定block或sector不能直接擦写操作;具体见数据手册第七章末尾的表格;

(S8-S7) SRP[1:0]:决定/WP控制状态寄存器的功能是否有效;是针对状态寄存器操作的配置;如下图所示:

(S9) QE:当置1后,表示为QSPI模式,且/WP引脚和/HOLD引脚功能无效,将对应引脚杜勇为QSPI数据引脚;

当QE为0时,/WP和/HOLD引脚功能有效;

QEbit需要先配置为1,然后执行Enter QPI(38h)指令,才能进入QPI模式;

(S13-S11) LB[3:1]:当置1后,对应的256bytes的security register永久性只读;是针对安全性寄存器的配置;

(S14) CMP:配合前面5bit一起配置非易失性保护;默认初始化为0;

(S15) SUS:当SUS为1时,表示执行完了擦写操作75h;当SUS为0时,表示执行完了擦写操作暂停指令7Ah;默认上电初始化为0;

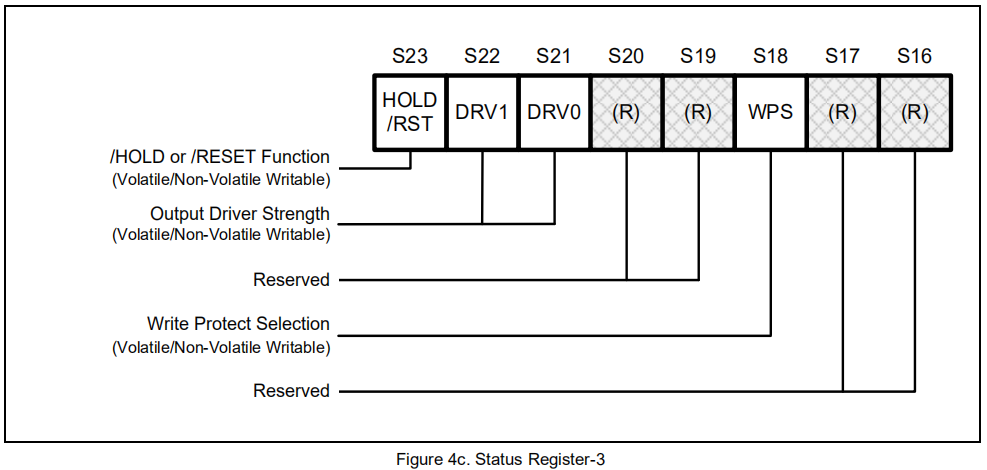

(S18) WPS:当WPS为0时,决定存储区域的非易失性写保护由寄存器的5bit决定;

当WPS为1时,表示存储区域的写保护通过发送指令来决定;具体见第7章末尾的表格;

(S22-S21)DRV[1:0]:用来决定驱动输出数据的强度,默认为11b,25%;

(S23) HOLD/RESET:默认为0,表示引脚功能为/HOLD;当配置为1时,表示引脚功能为/RESET;

4.3指令操作

芯片为SPI/DSPI/QSPI提供了45条基本指令。这些指令在CS拉低后便准备好接收了;数据传输高位在前先传输;

芯片为QPI提供了32条基本指令;QSPI接口仅支持从SPI接口使用38h指令切换过去,然后使用FFh切换回QSPI;

QSPI和QPI的主要差别在于QPI发送指令也是通过4线进行传输的,QSPI发送指令同SPI一样是通过1线进行传输的;

必须确保所写的地址范围内的数据全部为0XFF,否则在非0XFF处写入的数据将失败!

SPI的解码缓存是256字节,所以每次执行写操作的时候,写入数据的大小不大于256字节;

所以执行读写操作数据的时候都要先使能WEL,然后等BUSY位为0;