第三章 定时/计数技术

3.1 定时/计数

一、定时的分类

– 内部定时

计算机本身运行的时间基准或时序关系,使计算机每个操作都按照严格的时间节拍执行

(由CPU硬件结构确定,有固定的时序关系,无法更改 )

– 外部定时

外部设备实现某种功能时,在外设与CPU之间或外设与外设之间的时序配合

(由外设和被控对象的任务、功能决定,无一定模式,需要用户根据I/O设备的需求设定 )

二、定时方法

- 软件定时

– 基于CPU内部定时机构,运用软件编程

利用每执行一条指令需要若干个指令周期的原理,循环执行一段程序而产生等待延时,主要用于短时延时

– 优点

不需要增加设备,只需编制相应的延时程序以备调用

– 缺点

延时等待增加了CPU的时间开销,延时时间越长,等待开销越大,降低了CPU的效率,浪费了CPU的资源 - 硬件定时

– 采用可编程通用的定时/计数器或单稳延时电路产生的定时或延时

– 优点

硬件定时不占用CPU的时间,定时时间长,使用灵活,故得到广泛应用

3.2 可编程定时/计数器8253

可编程定时/计数器8253/8254

– 8253-5(5MHz),8254-2(10MHz),8253

(2MHz),8254(8MHz), 8254-5(5MHz)

– 3个独立的16位计数器

– 共有6种工作方式供选择

– 数据总线缓冲器和读写控制逻辑

– 外形、引脚、功能兼容,最高频率不同

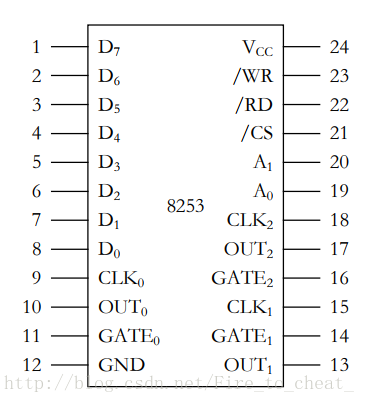

一、8253外部特性

– 8253是24引脚双列直插式芯片

– +5V供电

– 数据总线D0-D7,RD#和WD#分别是读写控制引脚,CS#是片选信号。A1,A0是片内地址选择引脚

– 8253的三个计数通道在结构上和功能上完全一样,每个通道均有两个输入引脚CLK和GATE,一个输出信号引脚OUT

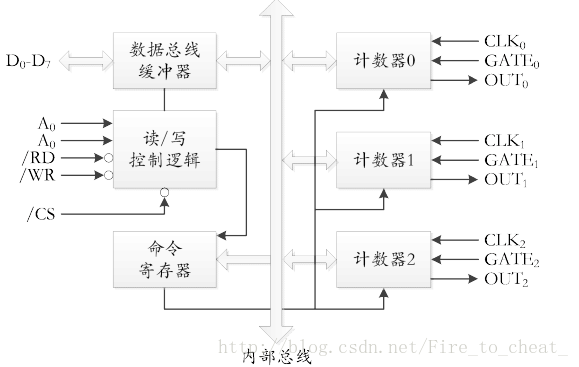

二、内部逻辑

- 8253内部逻辑结构

– 数据缓冲寄存器

– 读写逻辑

– 控制命令寄存器

– 计数器 - 计数通道内部逻辑

三、计数初值和编程命令

• 计数初值

– 计数初值寄存器用来寄存计数初值

– 计数工作单元为16位减1计数器,它的初值是计数初值寄存器内容

– 计数单元对CLK脉冲计数,每出现一个CLK脉冲,计数器减1,当减为零时,通过OUT输出指示信号表明计数单元已为零

– 作为定时器工作

当计数单元为零时,计数寄存器内容会自动重新装入计数单元,因为CLK输入是均匀的脉冲序列,所以OUT输出是频率降低了的脉冲序列(相对于CLK信号频率)

– 作为计数器工作

只关注在CLK端出现(代表事件)的脉冲个数,当CLK端出现了规定个数的脉冲时,OUT输出一个脉冲信号

• 计数器工作过程

1. 将控制字写入控制寄存器,指示8253的工作方式;

2. 将计数初值写入计数寄存器;

3. 计数单元开始工作,对CLK脉冲计数,每出现一个CLK脉冲,计数器减1;

4. 当计数单元减为零时,通过OUT输出指示信号表明计数单元已为零

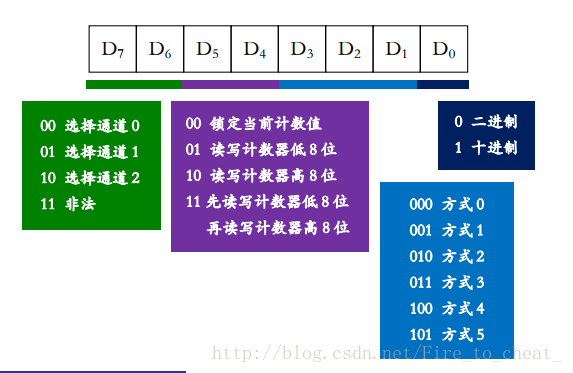

• 读写操作及编程命令

2种情况:写命令字操作、读当前计数值操作

工作方式命令字的格式

计算公式为:

Ci=CLK/OUT

Ci计数初值,CLK输入时钟频率,OUT输出时钟频率

• 读当前计数值(锁存后读操作)

在事件计数器的应用中,需要读出计数过程中的计数值,以便根据这个值做计数判断。为此,8253内部逻辑提供了将当前计数值锁存后

读操作功能。具体作法是:

1. 先发一条锁存命令(即方式控制字中的RL1RL0=00),将当前计数值锁存到输出计数器;

2. 执行读操作,得到锁存器的内容。

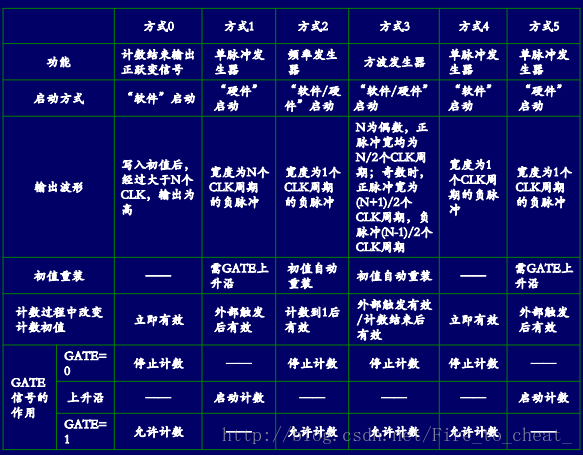

四、工作方式和特点

8253作为一个可编程计数器/定时器,可以用6种工作模式,不论工作在那种模式,都遵守下面几条基本规则:

1. 控制字写入寄存器时,所有控制逻辑电路立即复位,输出端OUT进入初始状态;

2. 初值写入后,要经过一个时钟上升沿和一个下降沿,计数执行部件才开始进行计数;

- 通常在时钟脉冲CLK的上升沿,门控信号GATE被采样

– 模式0,4中,门控信号为电平触发

– 模式1,5中,门控信号为上升沿触发

– 模式2,3中,门控信号为电平或上升沿触发(二种) - 在时钟脉冲CLK的下降沿,计数器作减1计数

– 0是计数器所能容纳的最大初始值

二进制时,0相当于216;BCD码时,0相当于104

工作模式决定以下内容

1. 门控信号的影响

– 高电平允许,当GATE=0,即使出现CLK,也不计数(模式0,2,3,4)

– 上升沿允许(上升沿触发)(模式1,5)

2. OUT信号的状态

– 写入控制字后

– 计数过程中

– 计数终了

3. 计数操作可否重复

– 不可重复(模式0,4)

– 自动重复(模式2,3)

– 条件重复(模式1,5)(GATE上升沿)

6种工作模式主要区别

– 输出波形不同

– 启动计数器的触发方式不同

– 计数过程中门控信号GATE对计数操作的影响不同

– 有的工作方式具备“初值自动重装”的功能

(当计数值减到规定的数值后,计数初值将会自动地重新装入计数器)

第七章 并行接口

7.2 可编程并行接口8255A

一、8255A的外部特性和内部结构

8255A的基本特性

- 具有两个8位(A口和B口)和两个4位(C口高/低4位)并行I/O端口的接口芯片

- 适应CPU与I/O接口之间多种数据传送方式

- 可执行功能强,3种工作方式,命令字内容丰富(方式字和控制字)灵活方便的编程环境,用户可根据外界条件使用8255A构成多种接口电路,组成微机应用系统(I/O设备需要哪些信号线以及它能提供哪些状态线)

- PC口的使用比较特殊,除作数据口外,当工作在1方式和2方式时,它的大部分引脚被分配作专用联络信号; PC口可以进行按位控制; 在CPU读取8255A状态时,PC口又作1,2方式的状态口用

- 8255芯片内部主要由控制寄存器、状态寄存器和数据寄器组成

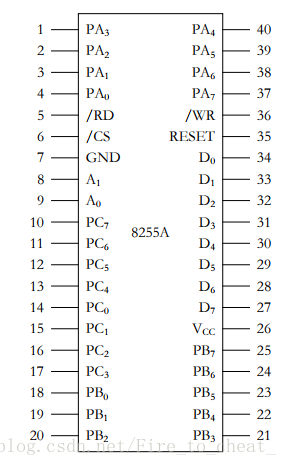

8255A的外部引线

– 外部引脚

①与系统总线的连接信号

面向数据总线:

D0-7 双向数据线,用于CPU向8255A发送命令/数据;8255A向CPU回送状态/数据

面向地址总线:A1,A0,/CS

面向控制的:

/RD:读信号,低电平有效

/WR:写信号,低电平有效

RESET:复位信号,高电平有效

- 清除控制寄存器并将8255A的A、B、C三个端

口均置为输入方式

- 输入寄存器和状态寄存器被复位

- 屏蔽中断请求

- 24条面向外设信号线呈现高阻悬浮状态

②与外部设备的连接信号

PA0-7 端口A的输入/输出线

PB0-7 端口B的输入/输出线

PC0-7 端口C的输入/输出线

24根信号线均可用来连接I/O设备和传送信息

– A口和B口只作输入/输出的数据口

C口的作用与8255A的工作方式有关,它除了作数据口以外,还有其他用途

- 数据口,PC4-7与A口一起组成A组, PC0-3与B口一起组成B组

- 状态口,区别于A口和B口不能作8255A本身的状态口

- 专用(固定)联络(握手)信号线

- 按位控制用,C口的8个引脚可以单独从1个引脚输出高电平

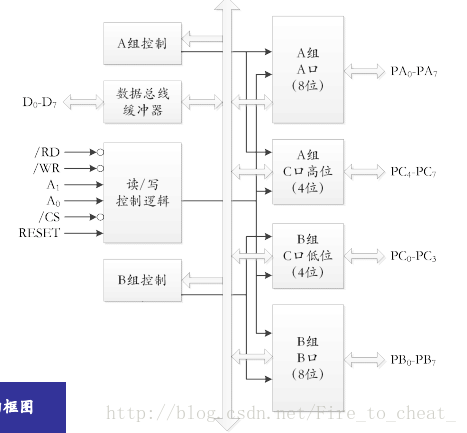

- 8255A的内部结构

① 数据总线缓冲器:三态双向8位缓冲器,8255A与CPU系统数据总线的接口

② 读/写控制逻辑:读/写控制逻辑由读信号RD,写信号WR,片选信号CS以及端口选择信号A1A0等组成

③ 输入/输出端口A/B/C:3个8位输入输出端口(port),每个端口都有一个数据输入寄存器和一个数据输出寄存器

④ A组和B组控制电路:控制A、B和C三个端口的工作方式

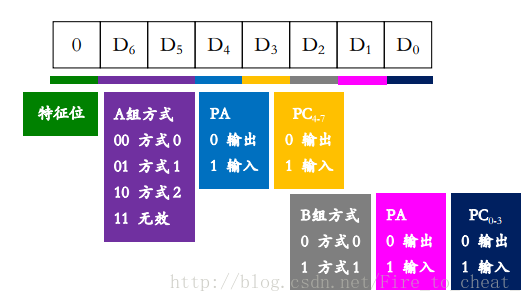

二、8255A的编程命令

方式命令

– 指定8255A的工作方式及其方式下3个并行端口(PA、PB、PC)的功能,是作输入还是作输出

– 最高位是特征位,必须写1

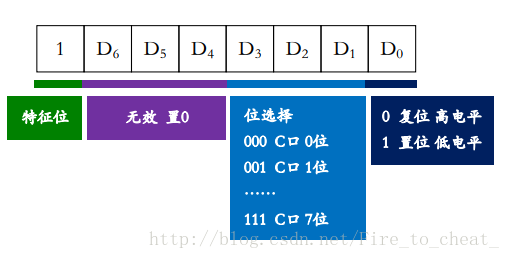

按位置位/复位命令

– 指定PC口的某一位(某一个引脚)输出高平或低电平

– 最高位是特征位,必须写

利用C口的按位控制特性还可以产生、负脉冲或方波输出,对外设进行控制

关于两个命令的讨论

① 方式命令指定8255A的3个端口的工作方式及功能,初始化工作在使用8255A之前进行

② 按位置位/复位命令只是对PC口的输出进行控制,不改变已经建立的3种工作方式,在初始化程序以后的任何时刻进行

③ 两个命令的最高位D7作为特征位,标识两个不同的命令;

④ 按位置位/复位的命令代码只能写入命令口A口/B口也可以按位输出高/低电平

– A口/B口的按位输出:以送数据到A口、B口来实现( 8255A的输出有锁存能力)

–C口按位输出:C口按位置位/复位命令以命令的形式送到命令寄存器执行

三、8255A的工作方式

8255A的工作方式与端口有关

– PA口有三种方式(0方式、1方式、2方式)

– PB口和PC口只有两种方式(0方式、1方式)

7.3 8255A的0方式及其应用

一、特点

1. 0方式是一种基本输入/输出工作方式,通常不用联络信号,或不使用固定的联络信号基本I/O方式采用查询方式(包括无条件传送)不能采用中断方式

2. 彼此独立的两个8位和两个4位并行口,都能被指定作为输入或者输出,共有16种不同的使用状态

3. 不设置专用联络信号线,需要联络时,由用户任意指定C口中的连线完成某种联络功能,不同于1方式、2方式下设置固定的专用联络信号线

– 端口与I/O设备之间无固定的时序关系

– 没有设置固定的状态字

4. 一次初始化只能指定端口PA/PB/PC作输入或输出,不能同时既作输入又作输出(单向I/O)

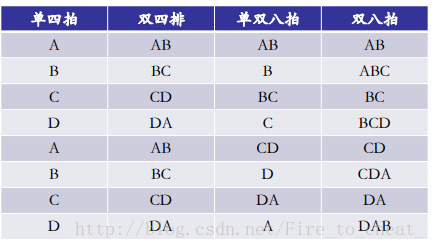

三、步进电机控制接口设计

1. 步进电机控制原理

步进电机是将电脉冲信号转换成角位移的一种

机电式数模转换器,步进电机旋转的角位移、

转速以及方向均受输入脉冲的控制

角位移与输入脉冲的个数据成正比

转速与输入脉冲的频率成正比

* 转动方向*与输入脉冲对绕组加电的顺序相关

2. 运行方式与方向的控制(循环查表法)

步进电机的运行方式是指各相绕组循环轮流通电的方式,例如,四相步进电机

– 为了实现对各绕组按一定方式轮流加电,需要一个脉冲循环分配器,可用硬件电路实现(控制字),也可用软件实现(循环查表法)

– 循环查表法,将各绕组加电顺序的控制代码制成一张步进电机相序表,存放在内存区,再设置一个地址指针

– 相序表的建立,要考虑两个因素:步进电机运行方式的要求,各相绕组与数据线连接的对应关系

3. 步进电机运行速度的控制(软件延时法)控制步进电机速度有两个途径:硬件改变输入脉冲的频率,通过对定时器(例如8253)定时常数的设定,使其升频、降频或恒频;软件延时,或调用延时子程序

4. 步进电机的驱动

步进电机在系统中是一种执行元件(带负载),需要功率驱动,在电子仪器和设备中,一般所需功率较小,常采用达林顿复合管作功率驱动

7.4 8255A的1方式及其应用

一、特点

① 1方式是一种选通输入/输出方式,即应答方式,需设置专用的联络信号线或应答信号线,对I/O设备和CPU两侧进行联络,通常用于查询(条件)传送或中断传送,数据的输入/输出都有锁存功能;

② PA和PB为数据口,PC口的大部分引脚分配作专用(固定)联络信号的引脚,用户不能再指定作其他作用;

③ 各联络信号线之间有固定时序关系,传送数据时,严格按照时序进行

④ 输入/输出操作过程中,产生固定状态字,作为查询或中断请求之用,状态字从PC口读取

⑤ 单向传送,一次初始化只能设置在一个方向上传送,不能同时作两个方向的传送

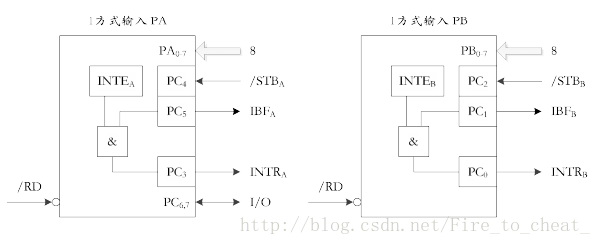

二、1方式下联络信号线的定义及其时序

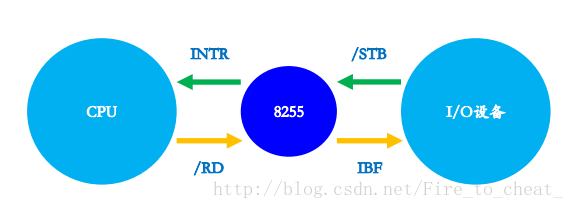

1. 输入联络信号线定义及时序

输入是从I/O设备向8255A送数据进来:I/O设备应先把数据准备好,并送到8255A,然后CPU从8255A读取数据 当A口和B口为输入时,各指定了C口的3根线作为8255A与外设及CPU之间应答信号:

* STB#* 外设给8255A的“输入选通”信号,低电平有效

**IBF **8255A给外设的回答信号“输入缓冲器满”,高电平有效

* INTR* 8255A给CPU的“中断请求”信号,高电平有效

① 数据输入时,外设处于主动地位,当外设准备好数据并放到数据线上后,首先发/STB信号,由它把数据输入到8255A;

② 在/STB的下降沿约300ns,数据已锁存到8255A的缓冲器后,引起IBF变高,表示8255A的“输入缓冲器满”,禁止输入新数据;

③ 在/STB上升沿约300ns后,在中断允许(INTE=1)的情况下IBF的高电平产生中断请求,使INTR上升变高,通知CPU,接口中已有数据,请求CPU读取;

④ CPU得知INTR信号有效之后,执行读操作时,/RD信号的下降沿使INTR复位,撤消中断请求,为下一次中断请求作好准备

二、1方式下联络信号线的定义及其时序

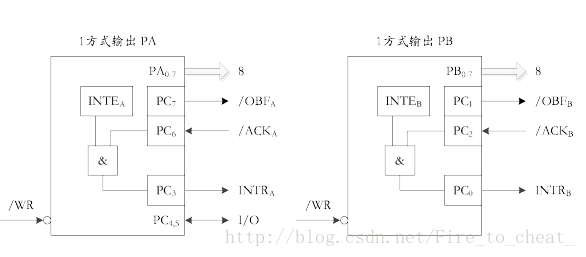

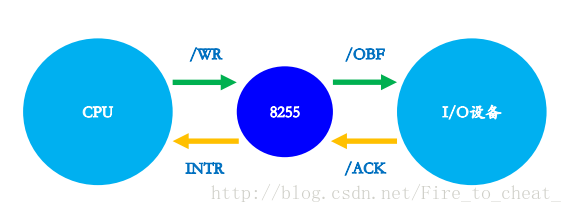

2. 输出联络信号线定义及时序

输出是8255A送数据到I/O设备:CPU先把数据准备好,并送到8255A,然后8255A把数据输出去

当A口和B口为输出时,各指定了C口的3根线作为8255A

与外设及CPU之间应答信号:

OBF# 8255A给外设的回答信号“输出缓冲器满”,低

电平有效

ACK# 外设给8255A的“回答”信号,低电平有效,外设已经从8255A的端口接收到了数据

INTR 8255A给CPU的“中断请求”信号,高电平有效

① 数据输出时,CPU应先准备好数据,并把数据写到8255A输出数据寄存器,当CPU向8255A写完一个数据后,WR#的上升沿使OBF#有效,表示8255A的输出缓冲器已满,通知外设读取数据,并且WR#使中断请求INTR变低,复位中断请求;

② 外设得到OBF#有效的通知后,开始读数,当外设读取数据后,用ACK#回答8255A,表示数据已收到;

③ ACK#的下降沿将OBF#置高,使OBF无效,表示输出缓冲器变空,为下一次输出作准备,在中断允许(INTE=1)的情况下ACK上升沿使INTR变高,产生中断请求,CPU响应中断后,在中断服务程序中,

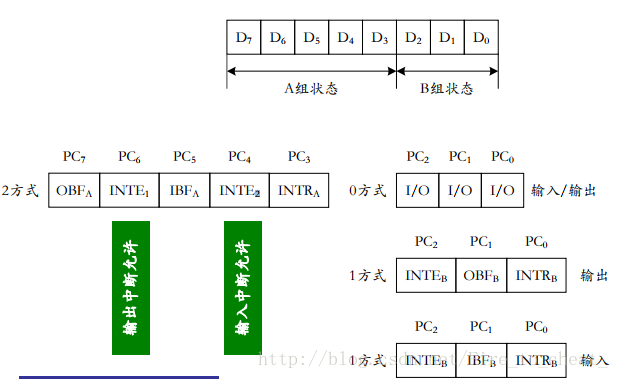

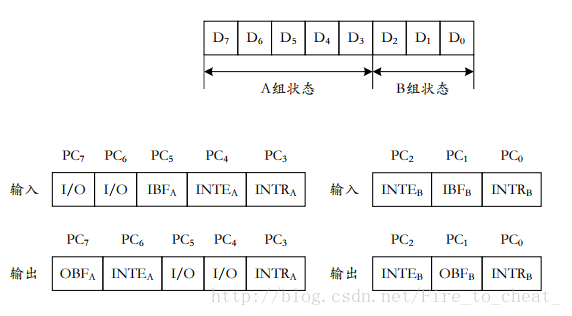

三、1方式的状态字

1. 状态字的作用

在1方式下8255A有固定的状态字,为查询方式提供了状态标志位IBF和OBF;当8255A采用中断方式:CPU可以通过读状态字来确定中断源,实现查询中断(例如单片机系统);也可以采用中断控制器来确定中断源,实现向量中断(例如PC系统)

2. 状态字的格式

分A和B两组,A组状态位占高5位,B组状位占低3位,输入和输出时的状态字不相同

3. 使用状态字时要注意的几个问题

① 状态字在8255A输入/输出操作过程中由内部产生,从C口读取的,与C口的外部引脚无关

(输入:PC4=>INTE(A) PC2=>INTE(B))

(输出:PC6=>INTE(A) PC2=>INTE(B))

② 状态字中供CPU查询的状态位有:IBF位和INTR位(输入时);OBF位和INTR位(输出时)

在1方式下采用查询方式时,一般查询状态字中的INTR位

③ 状态字中的INTE是控制标志位,控制8255A能否提出中断请求,不是I/O操作过程中自动产生的状态,由程序通过按位置位/复位命令设置或清除

四、1方式的接口设计方法

– 首先根据实际情况确定A、B两口是输入还是输出,然后把C口分配作联络的专用应答线与外设相应的状态线和控制线相连

– 注意当使用中断方式和查询方式时,INTR的连接

• 中断方式:INTR接微处理器或中断控制器

• 查询方式:INTR不连接,查状态字中的INTR状态位

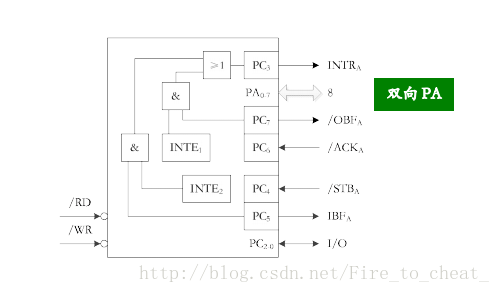

7.5 8255A的2方式及其应用

一、特点

① PA口为双向选通输入/输出或叫双向应答式输入/输出:一次初始化可指定PA口既作输入口又作输出口

② 设置专用的联络信号线和中断请求号信线,可采用中断方式和查询方式与CPU交换数据。

③ 各联络线的定义及其时序关系和状态基本上是在1方式下输入和输出两种操作的组合

二、2方式下联络信号线的定义及其时序

1. 联络信号线的定义

2方式是一种双向选通输入输出方式,将A口作为双向输入/输出口,将C口的5根线作为专用应

答线PC3-7

8255A只有A口才有2方式

2. 引脚定义

3. 工作时序

三、2方式的状态字

2方式的状态字的含义是在1方式下输入和输出状态位的组合

第十章 A/D与D/A转换器接口

10.1 D/A转换器的接口方法

一、D/A转换器主要参数

D/A转换器一般是根据自己的需要选择相应数据位宽度和速度的D/A转换芯片,在选择D/A转换器芯片时一般考虑如下指标

- 分辨率 D/A转换器能分辨的最小电压增量,或1个二进制增量所代表的模拟量大小,DAC能转换的二进制数的位数越多,分辨率越高

分辨率表示为:分辨率=Vref/2位数,例如,Vref=5V,8位的D/A转换器分辨率为5/256=20mV

- 转换时间 数字量输入到模拟量输出达到稳定所需的时间。

电流型:100ns~1µs;

电压型:运算放大器的响应时间(较慢)

- 精度 D/A转换器实际输出与理论值之间的误差,一般采用数字量的最低有效位作为衡量单位(1/2 LSB)

例如,8位D/A分辨率为20mV,则精度为±10mV

- 线性度 当数字量变化时,输出模拟量按比例变化的程度

- 线性误差 模拟输出偏离理想输出的最大值

二、D/A转换器的连接特性

DAC(数字/模拟转换集成电路)是系统或设备中的一个功能器件,当将它接入系统时,不同的应用场合对其输入输出有不同的要求

- 输入缓冲能力 DAC的输入缓冲能力是非常 重要的,具有缓冲能力(数据寄存器)的DAC芯片可直接与CPU或系统总线相连,否则必须添加锁存器

- 输入数据的宽度(分辨率) 8位,10位,12位,16位,当DAC的分辨率高于微机系统的 数据总线的宽度时,需要分两次输入

输入数据码制 对于单极性输出的DAC只能

接收二进制或BCD码;双极性输出的DAC只

能接收偏移二进制码或补码

- 输出模拟量的类型 DAC输出有电流型(电流大小位于几毫安到十几毫安)和电压型(电压大小一般位5~10V)两种,用户可根 据需要选择,也可采用其它器件进行转换

- 输出模拟量的极性 DAC有单极性和双极性两种,如果要求输出有正负变化,则必须使用双极性DAC芯片

三、DAC典型连接

DAC芯片与CPU或系统总路线连接时,可从数据总线宽度是否与DAC位数据匹配和DAC是否具有数据寄存器两个方面来虑

- 当DAC位数与数据总线宽度相同,并具有数 据缓冲能力时,可直接与CPU连接

- 当DAC位数与数据总线宽度相同,DAC没有数据寄存器时,必须外加锁存器或I/O接口芯片(例如8255A等)才能与CPU连接

- 当DAC位数大于数据总线宽度,DAC无论有无数据寄存器时,都必须外加锁存器或I/O接口芯片才能与CPU相连接

10.2 D/A转换器的接口设计

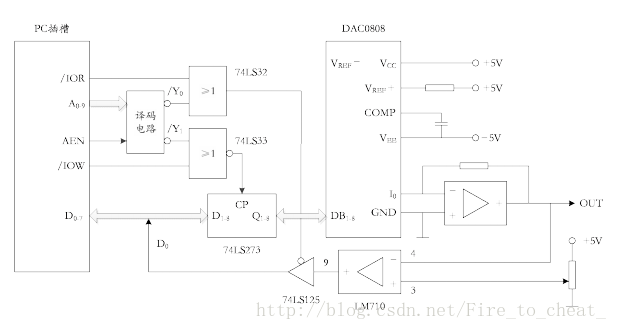

一、片内无三态输入缓冲器的8位D/A

要求 用DAC0808构成一个直流数字电压表,端口地址位318H,319H

分析

- DAC0808,8位,无三态缓冲能力,需要外加数据锁存器

- 数字量由DAC0808转换成电压量,与输入电压(需要测量的电压)比较,若输入电压比n对应电压大,但n+1对应电压小,则结果为n或n+1

- 硬件连接

- 软件编程:采用逐次逼近的方法寻找数字量结果,二分搜索法每次确定区间的中间值去试探

二、片内有三态输入缓冲器的8位D/A

- 要求

产生任意波形,用DAC0832产生三角波、方波、锯齿波或梯形波等 - 分析

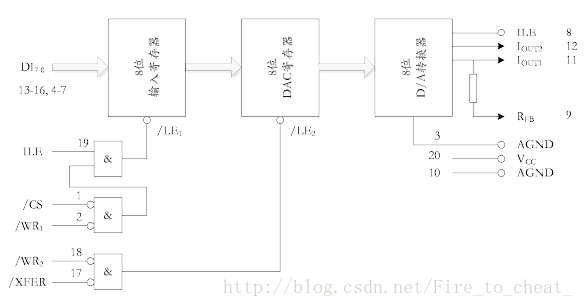

8位,具有两级缓冲寄存器(输入寄存器 & DAC寄存器)

当ILE=1,CS#=WR1#=0,写入第1级缓冲器;

当XFER#=WR2#=0,写入第2级缓冲器,并开始转换; - 应用

适合要求多片DAC同时进行转换的系统

三种工作方式

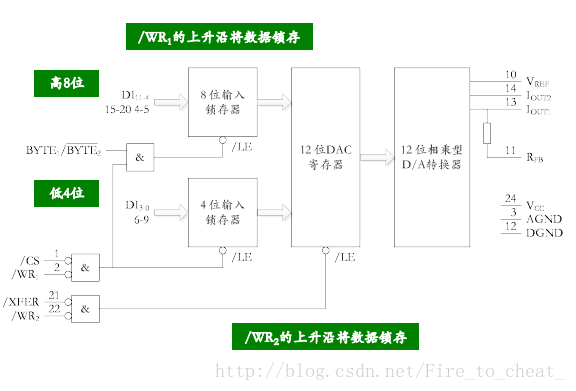

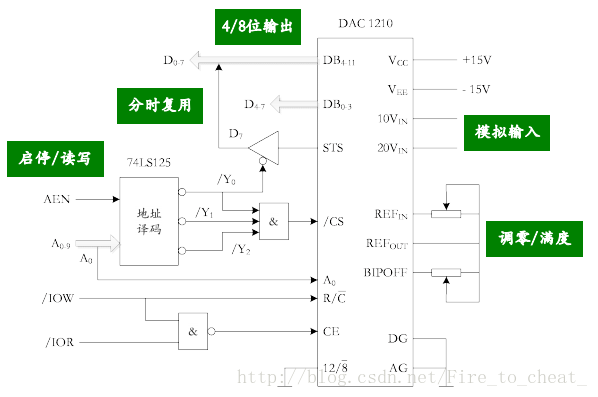

三、12位D/A转换器接口设计

- 片内无三态输入缓冲器

- 片内有三态输入缓冲器的

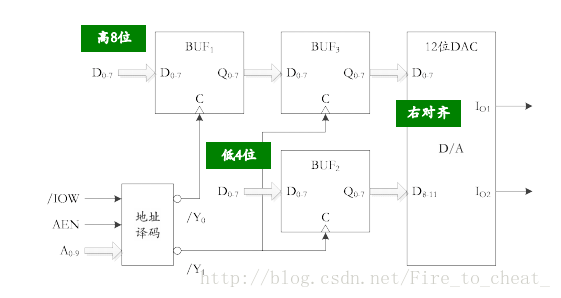

由于微机的I/O指令一次只能输出8位数据,因此对于数据宽度大于8位DAC只能分两次输入数据,为此一般大于8位数据宽度的DAC内部均设计有两级数据缓冲,例如,12位DAC1210内部有两级数据缓冲

四、D/A转换器应用

- 函数DAC可以产生任意波形、幅度和频率的信号,如三角波、方波、函数波等

- 用DAC来构成ADC的应用

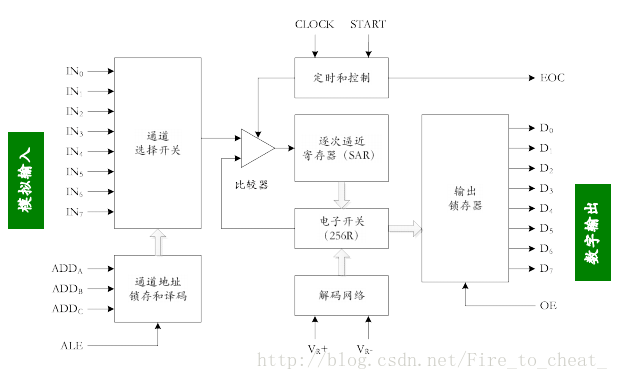

10.3 A/D转换接口基本原理与方法

一、A/D转换原理

– 在数据采集和过程控制中,被采集对象往往是连续变化的物理量(如温度、压力、声波等),由于计算机只能处理离散的数字量,需要对连续变化的物理转换为数字量,这一操作过程就是A/D转换

– A/D转换的原理很多,常见的有双积分式、逐次逼近式、计数式等,输出码制有二进制、BCD码等,输出数据宽度有8位、12位、16位、20位等(二进制)和3+1/2位(最大为1999)、5+1/2位等(BCD码),该过程就是A/D转换

二、A/D转换器特性

– 分辨率 指A/D转换器可转换成数字量的 最小电压(量化阶梯),例如,8位ADC满量程为5V,则分辨率为5000mV/256=20mV,即当模拟电压小于20mV,ADC就不能转换了。分辨率一般表示式为:分辨率=Vref/2位数(单 极性)

– 转换时间 指从输入启动转换信号到转换结束,得到稳定的数字量输出的时间。一般转换速度越快越好(特别是动态信号采集),常见有超高速(转换时间<1ns)、高速(转换时间<1µs)、中速(转换时间<1ms)和低速(转换时间<1s)等

如果采集对象是动态连续信号,要求f采≥2f信, 也就是说必须在信号的一个周期内采集2个以上 的数据,才能保证信号形态被还原,这就是“最 小采样”原理,若f信=20kHz,则f采≥ 40kHz,其转换时间要求≤25µs

– 量化精度 指A/D转换器实际输出与理论值之间的误差,一般采用数字量的最低有效位作为衡量单位(如1/2 LSB)

– 线性度 当模拟量变化时,A/D转换器输出的数字量按比例变化的程度

二、外部特征

– 模拟信号输入线(单通道/多通)

– 数字量输出线

– 启动输入线

– 转换结束线

几种A/D芯片的对照表

三、接口方法

- A/D转换器与CPU的连接

– A/D转换器的分辩率

– 是否有输出锁存器

– 启动信号(电平启动/脉冲启动) 接口的主要的操作

– 进行通道选择

– 发转换启动信号

– 取回“转换结束”状态信号

– 读取转换的数据

– 发采样/保持(S/H)控制信号(高速A/D)A/D转换器数据的传送

– 对于查询方式

– 对于中断方式

– 对于DMA方式

– 对于超高速数据采集系统A/D转换电路的接口形式

– 与CPU直接相连

当ADC芯片内部带有数据输出锁存器和三态门时

(例如AD574、ADC0809等),它们的数据输出可直接与CPU或数据总线相连

– 用三态锁存器与CPU相连

(例如ADC1210、AD570等),需外接三态锁存器后才能与CPU或系统总线相连

– 通过I/O接口芯片与CPU相连

无论ADC内部有无数据锁存器,都可以通过I/O接口芯片(并行或串行)与CPU或系统总线相连的,这样可简化接口电路

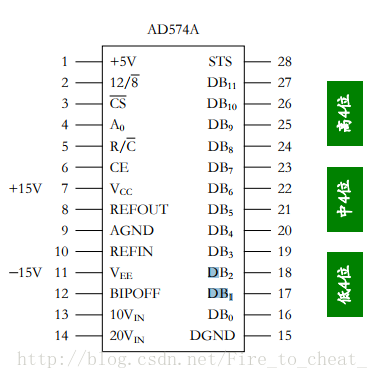

一、12位ADC连接与编程

– ADC574A是具有三态输出锁存器的12位逐次比较ADC芯片,转换速度快(25ms),是目前国内使用最广泛的ADC芯片之一

– ADC574A可并行输出12位数据,也可以分两次输出(高8位+低4位)数据;既可进行8位转换,也可进行12位A/D转换

– ADC574的控制信号

– ADC574的引脚定义

– ADC574的工作时序

二、12位A/D转换器接口设计

- 要求

进行12位转换,转换结果分两次输出,以左对齐方式存放在首址为400H的内存区,共采集64个数据,ADC与CPU之间采用查询方式交换数据,采用AD574A作为A/D转换器 - 分析

AD574A是具有三态输出锁存器的A/D转换器, 它可以作12位转换,也可作8位转换 设计

– 硬件连接

– AD574内部有三态输出锁存器,数据输出线可直接与系统数据线相连,将AD574A的12条输出数据线的高8位接到系统总线的D0~D7,而把低4位接到数据总线的高4位,低4位补0,以实现左对齐

– 转换结束状态信号STS,通过三态门74LS125接到数据线D7上;因为分两次传送,所以将12/8#接数字地;CE接VCC,允许工作

I/O端口地址译码( A0-9 )三个端口地址

Y0=310H,状态口

Y1=311H,控制口(8位)/数据口(低4位)

Y2=312H,控制口(12位)/数据口(高8位)

说明

– A/D转换采集程序一般采用中断方式或线程

方式编写(多任务操作系统),用软件查询 方式可能会导致数据丢失,因此使用较少

10.5 中断方式的A/D转换接口电路设计

一、PC机系统的中断方式数据采集系统设计

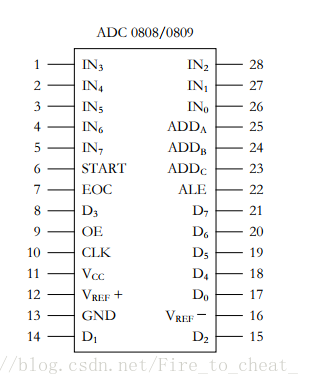

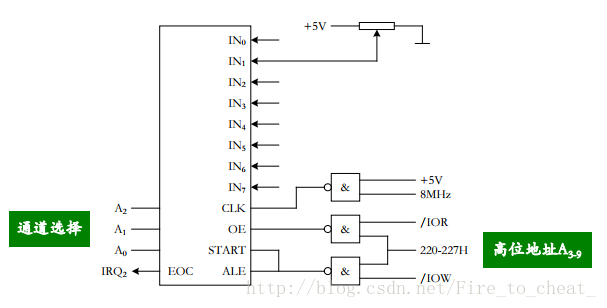

- 8位ADC连接与编程

– 逐次逼近式8位ADC芯片ADC 0809

– START是ADC0809的A/D转换启动信号,高电平时内部逐次逼近寄存器清0,由1 → 0变化时开始A/D转换,信号宽度>100ns,CLK为时钟信号,最大为600KHz

– 硬件连接电路如图

– 设地址译码/CS为220H至227H,采用中断方式的采集程序如下

10.6 DMA方式的A/D转换接口电路设计

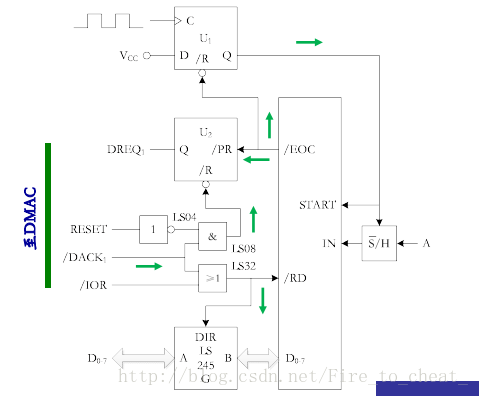

一、采用DMA方式的A/D转换器接口电路分析与设计

- 要求

使用8位A/D转换器,共采集4K个字节数据,采集的数据用DMA方式,送到从30400H开始的内存保存,以待处理,内存地址以+1方式修改。使DMAC8237A-5的通道1,单一传送方式。 - 电路分析与设计

根据上述要求,采用下图所示的电路可以实现DMA方式的数据采集任务

二、初始化编程 - 分析

在PC机系列微机中,由于BIOS已对8237A-5进行了初始化,故用户程序并不需要对所有16个寄存器逐一编程,根据题意只涉及以下几个操作及对应的寄存器

① 选定传送通道及工作方式,使用工作方式及对应的寄存器

② 设置DMA屏蔽字,使用屏蔽寄存器,端口 = 0BH

③ 设定传输的总字节数,使用字节数寄存器,端口 = 03H(通道1)

④ 设定传送的存储器地址,使用地址寄存器,端口 = 02H(通道1)

⑤ 写清除先/后触发器,使用地址寄存器,端口 = 0CH - 编程