参考文档

I2S

I2S硬件接口分为三种工作模式:

- I2S Phillips Standard I2S模式

- Left Justified Standard 左对齐模式

- Right Justified Standard 右对齐模式

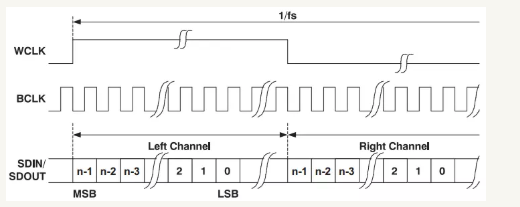

I2S模式

左对齐模式

右对齐模式

备注

MSB表示数据的最高BIT位,LSB表示数据的最低BIT位。

I2S模式属于左对齐模式中的一种特例,由左对齐模式数据延迟一个BCLK时钟周期变化而来。

左对齐模式:左声道数据MSB在WCLK上升沿之后BCLK的第一个上升沿有效;右声道数据MSB在WCLK下降沿之后SBCLK第一个上升沿有效。

右对齐模式:左声道数据LSB在WCLK下降沿前一个BCLK上升沿有效,右声道数据LSB在WCLK上升沿前一个BCLK上升沿有效。

左右对齐模式LRCK/WS高电平对应左声道,低电平对应右声道;而I2S模式低电平对应左声道,高电平对应右声道。

PCM

PCM硬件接口上传输的是PCM编码的数据,I2S上传输的也是PCM编码的数据,I2S不过是PCM接口的特例。

I2S接口的工作模式有统一的标准,但是PCM接口工作模式没有统一的标准,支持更加灵活的传输协议。

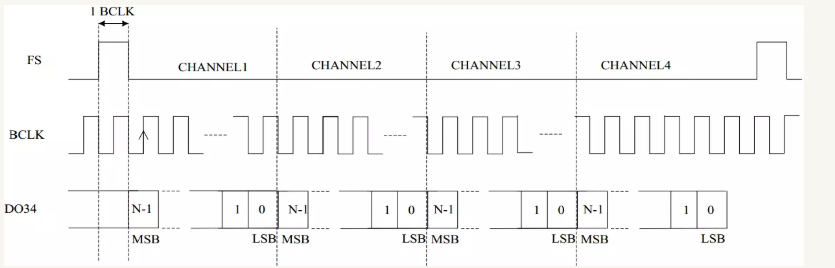

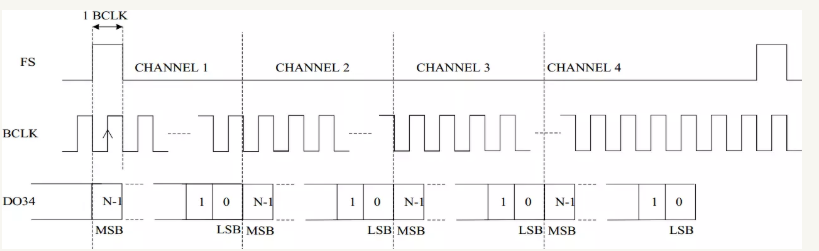

PCM接口分为两种常用操作模式:DSP A mode和DSP B mode,统称为DSP mode。

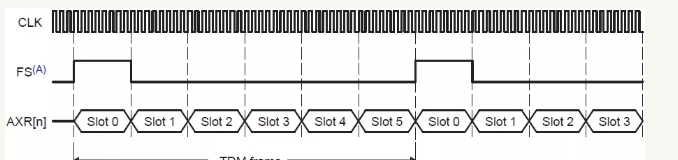

基于DSP mode,PCM接口可以配置支持TDM(Time Division Multiplexing)数据传输。可以支持传输多个声道的数据,允许多个设备同时使用总线。由于没有统一的标准,不同厂商在TDM 实现的时序上略有差异。

DSP A: FSYNC有效后,数据在BCLK的第2个上升沿(下降沿)有效(one bit clock delay)

DSP B: FSYNC有效后,数据在BCLK的第1个上升沿(下降沿)有效(no delay)

在DSP B模式内,数据延迟一个bit clock周期有效就是DSP A模式。可见A是B的特例。

DSP A

DSP B

长短帧模式

在mode B中,根据FYNC信号脉冲宽度的不同,PCM帧同步时钟工作模式大致分为长帧同步模式和短帧同步模式。

长帧同步模式:FSYNC脉冲宽度等于1个Slot的长度。Slot在TDM中表示的是传输单个声道所占用的位数。注意,Slot的位数并不一定等于音频的量化深度。比如Slot可能为32 bit,其中包括24 bit有效数据位(Audio Word) + 8 bit零填充(Zero Padding)。

长帧同步模式

短帧同步模式:FSYNC脉冲宽度等于1个BCLK时钟周期长度。