Design For testability

DFT(Design for Test):可测试性设计(DFT)是一种集成电路设计技术,它将一些特殊结构在设计阶段植入电路,以便设计完成后进行测试。电路测试有时并不容易,

这是因为电路的许多内部节点信号在外部难以控制和观测。通过添加可测试性设计结构,例如扫描链等,内部信号可以暴露给电路外部。

总之,在设计阶段添加这些结构虽然增加了电路的复杂程度,看似增加了成本,但是往往能在测试阶段节约更多的时间和金钱。

DFT的理念基于 结构化测试(分治法)。它并不是直接对芯片的逻辑功能进行测试来确保功能正常。而是尽力保证电路之间的低层级模块和它们之间的连接正确。

或者说,模块和网表在布局布线为实际电路的制造过程中没有错误。举个例子就是,我们检测完网表和模块实现是正确的,那么我们就认为DFT测试通过。

这一点和功能测试区别很大。这个理念极大地减少了测试的工作量,同样也和FPGA的set up debug wire有着异曲同工之妙。

DFT的关键也就在于取舍,测试逻辑的代价和效果的平衡。核心目的在于提高Observability 和Controllability。

DFT主要负责制造时产生的缺陷检测,逻辑上的错误鞭长莫及。具体例子就是芯片挑体质。

在RTL设计阶段开始介入,设计插入DFT逻辑,设计并验证测试向量(功能仿真),综合时序也要收敛,

得到芯片后进行机台调试。

DFT有三种主流的方法,SCAN,MBIST(Memory built in self-test)和Boundary scan.

它们分别针对寄存器、memory/ip核、chip互联。

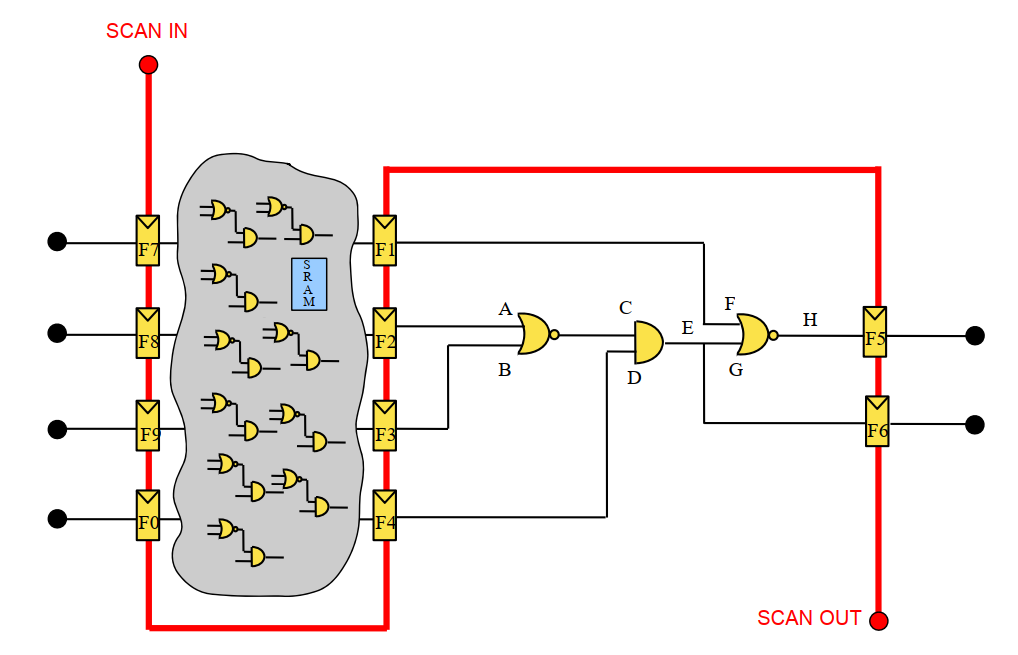

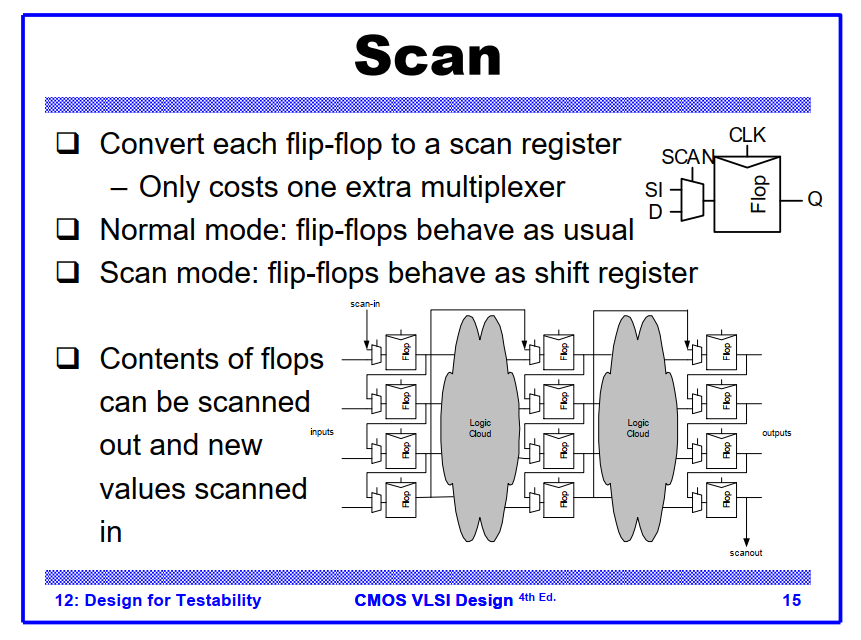

Scan技术(扫描链插入和基于扫描链的ATPG(Automatic Test Pattern Generation),自动测试向量生成)

其核心是基于扫描结构的触发器。ATPG基于自动生成test vector的tool。

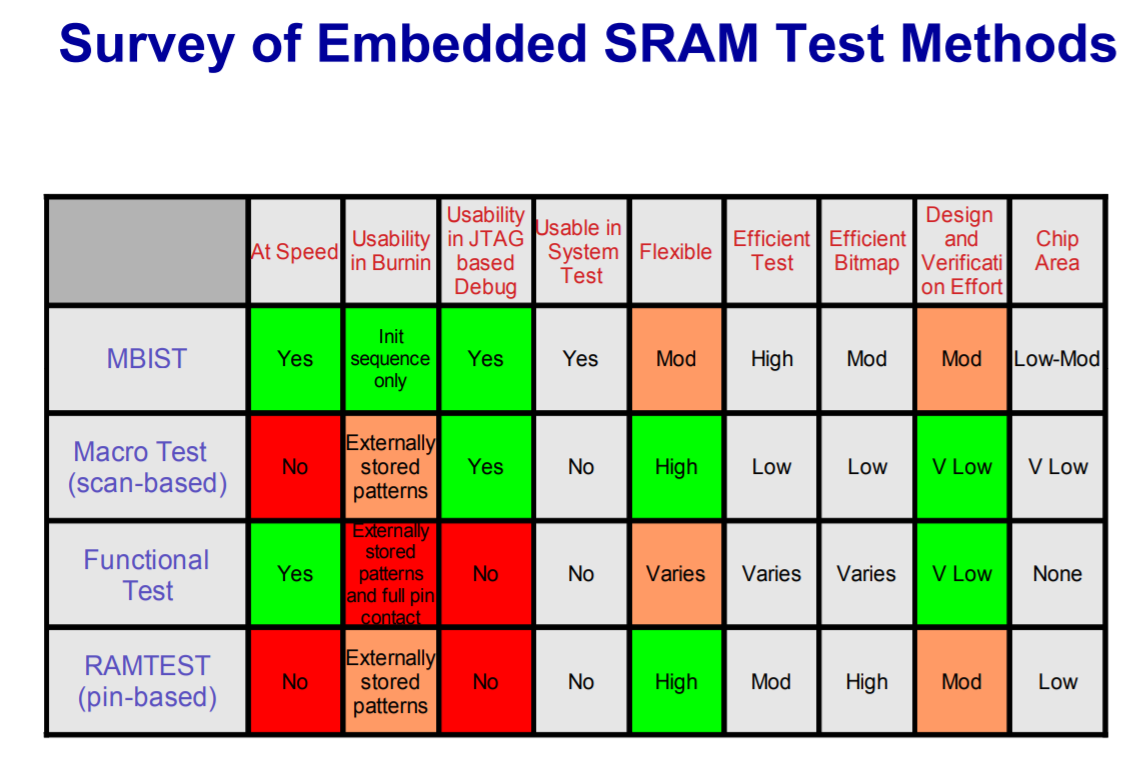

BIST,顾名思义Build In Self-test。自动生成随机的输入给到组合逻辑,根据组合逻辑的输出判断是否有问题。下图是MBIST和其他SRAM测试方式的对比。

Boundry scan 涉及到一个JTAG协议,还有Boundary Scan cell。Jtag是IEEE的一个标准协议,包括5个引脚。

- TCK——测试时钟输入;

- TDI——测试数据输入,数据通过TDI输入JTAG口;

- TDO——测试数据输出,数据通过TDO从JTAG口输出;

- TMS——测试模式选择,TMS用来设置JTAG口处于某种特定的测试模式。

- 可选引脚TRST——测试复位,输入引脚,低电平有效。

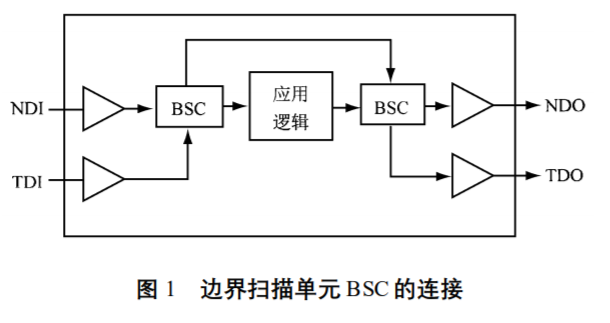

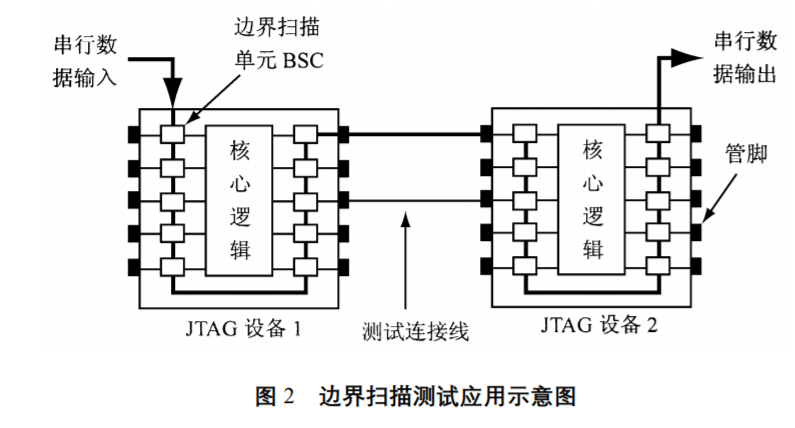

边界扫描测试是通过在芯片的每个 I/ O 脚附加一个边界扫描单元 (BSC ,boundary scan cell) 以及一些附加的测试控制逻辑实现的,BSC主要是由寄存器组成的。每个I/ O管脚都有一个 BSC ,每个BSC有两个数据通道 :一个是测试数据通道 ,测试数据输入TDI (test data input) 、测试数据输出TDO (test data output) ;另一个是正常数据通道,正常数据输入NDI ( normal data input ) 、正常数据输出 NDO (normal data output) 。

在正常工作状态,输入和输出数据可以自由通过每个BSC,正常工作数据从NDI进,从NDO出。在测试状态,可以选择数据流动的通道:对于输入的IC(集成电路,integrated circuit)管脚,可以选择从NDI或从TDI输入数据;对于输出的IC管脚,可以选择从BSC输出数据至NDO,也可以选择从BSC输出数据至TDO。

图2所示是边界扫描测试应用的示意图。为了测试两个JTAG设备的连接,首先将JTAG设备1某个输出测试脚的BSC置为高或低电平,输出至NDO,然后,让JTAG设备2的输入测试脚来捕获从管脚输入的NDI值,再通过测试数据通道将捕获到的数据输出至TDO,对比测试结果,即可快速准确的判断这两脚是否连接可靠。

FPGA中也有类似的设计,就是set up debug(在综合以后)。假如对某根信号线设置为true,那么Vivado会使用额外的逻辑和布线资源来构造额外的电路

来采集这个信号。通过设置采样深度(一般1024T)我们就能得到这个信号的运行情况。最后再布局布线,生成bit流文件烧入FPGA。

同样会增加布线压力,消耗逻辑、布线以及存储资源。注意,输入和输出信号不能设为debug,要加buffer。