差分标准

和单端IO不同的是,差分电平使用两根信号线来传达信号,这两根信号线在传输过程中如果遇到同样的噪声源(共模噪声)干扰,在接收端,这样的共模噪声会在两个信号相减时消除,这样并不会给接收电平造成影响。

在单端信号的传输过程中,信号往往以电源平面或地平面作参考平面,而在差分电平中,由于两根线的电流方向相反,因此两者产生的电磁场相互抵消。向外辐射的地磁波更少,也就是减小了EMI,同样也减小了对参考平面的依赖,在传输过程中,两根电流大小一样,方向相反的信号线互为参考。不过,信号线与电源平面或地平面之间的距离等因素会影响信号线的差分阻抗。

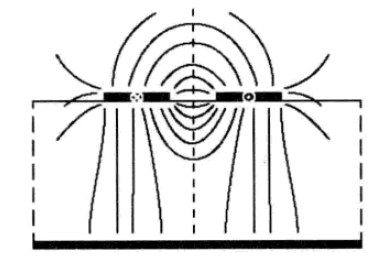

下图所示,可以明显地看到两个差分信号线之间的电磁场。由于两者的电流大小相等,方向相反,于是他们之间的电磁场相互抵消,同时减少了对外的辐射。两者之间的电磁场越强,对外辐射也就越小。

微带线(microstrip)

带状线(stripline)

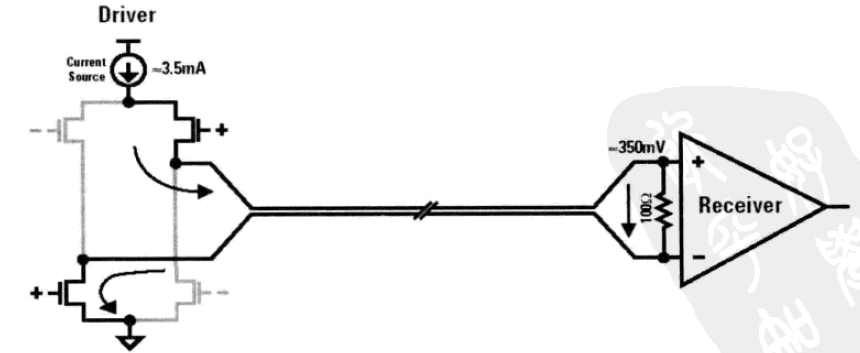

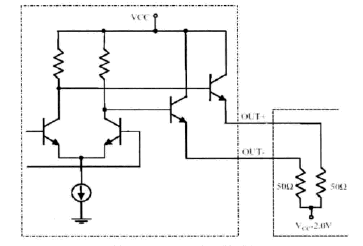

LVDS是一种常见的差分电平,如下图:

LVDS驱动器和接收器

在LVDS驱动器中,采用一个恒流源(大约3.5mA)输出,由于输入端的输入阻抗非常高,绝大部分的驱动电流流经100欧姆电阻,因此在接收器的输入端,两个信号线之间,产生了一个100*3.5=350mV的输入电压。当驱动器的输入电平翻转时,流经100欧姆电阻的电流方向就发生了变化,于是就会在电阻两端形成“0”和“1”两种逻辑状态。

和LVTTL/LVCMOS标准直接输出电压幅度信号不同的是,LVDS的驱动器输出是电流信号,由电流信号在接收端的差分匹配电阻上产生了一个合适的电压幅度信号,作为接收器的判决电平。因此,业界也把这种驱动器叫做电流模式(current mode)驱动器。

电压模式的驱动器,在静态时可以认为其输出的电流为0,而信号在翻转时,会产生较大的瞬态电流(Icc),Icc的大小随着时钟频率的增加而成指数增加,会给系统引入较大的开关噪声,尤其是在信号的边沿比较陡的时候,这种问题尤为严重。而电流模式的驱动器就不存在这种问题,LVDS的驱动器从电源汲取的电流值是恒定的大约3.5mA,无论信号如何翻转,这个电流值时钟不变,只是其在传输信号上的方向不同而已。而且LVDS的信号边沿相对比较缓,对保持信号完整性也是有好处的。

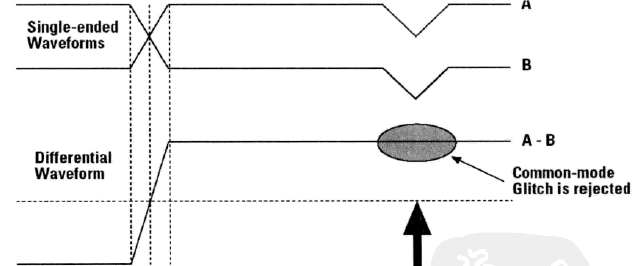

单端标准的信号一般是以地做参考,输出一定幅值的电压信号。而差分信号的输出有一个固定的共模输出电压(Vocm),如LVDS是1.2V,正端和负端的信号都是在这个共模电压的上下来回摆动的。在差分输入端,信号的输入共模电压允许在一定范围之内,如LVDS的信号输入的电平允许的值是0~2.4V,这样即使信号在传输过程中出现较大的共模干扰,也会在接收端相互抵消,如下图:

共模噪声的抵消

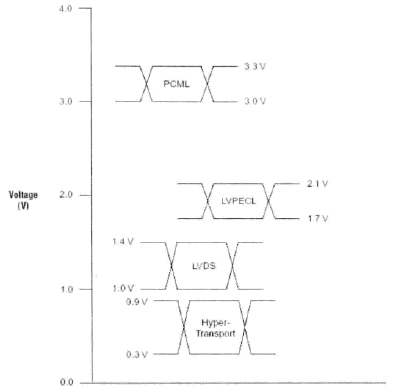

下图所示为几种差分电平标准的共模输出电压和输出摆幅示意图。

差分电平输出幅度示意图

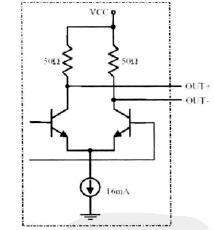

与LVDS相比,LVPECL电平的输出结构是一对射极跟随器(emitter follower),它的特点是翻转速度很快,但是直流电流很大,大概为14mA。LVPECL的驱动器的输出阻抗很小,因此其驱动能力非常强,如下图:

LVPECL驱动器结构

CML也是一种常用的差分电平标准,其驱动器又一个共射极差分对直接输出。CML电平常用在高速的网络和通信设备中,其串行数据速率可以做到非常高,如10Gbit/s,如下图:

CML驱动器结构

对差分信号加终端电阻时,也可以采用FLY-BY的布PCB线,以尽量减少由于匹配电阻造成的短线,影响信号质量,如下图:

差分匹配的FLY-BY方式

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间