提到DDRII,大家应该都不陌生,DDRII SDRAM是第二代双倍速率同步动态RAM。今天小编给大家介绍一下QUARTUS II 下调用DDRII软核。

新建QUARTUSII工程之后,在tool下找到Megawizard plug-in manager,新建自定义宏功能模块 。

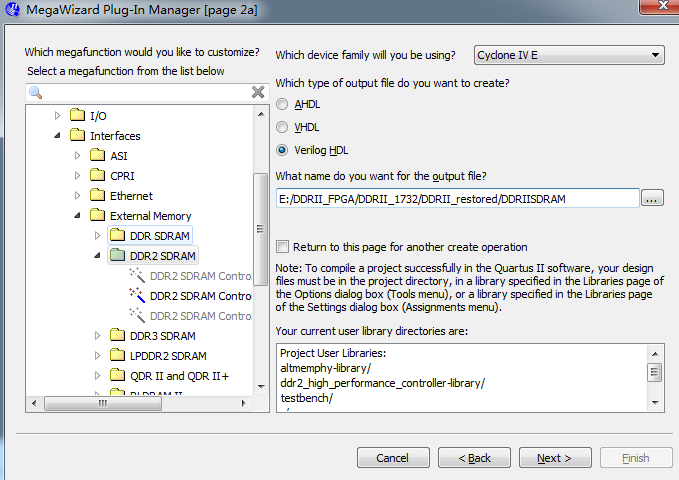

如上图,注意在interface下选择external memory,DDR2SDRAM,语言选择verilog hdl,输出文件名字填写相应的模块名。

如上图,输入参考时钟50M,根据自己的实际输入频率填写,此时钟为DDRII软核内部PLL输出时钟。存储器时钟频率根据自己要求填写,以小编的开发板EP4CE15F17为例,此FPGA上跑DDRII的时钟频率为125M-167M。最下面的控制数据速率,分为全速和半速。

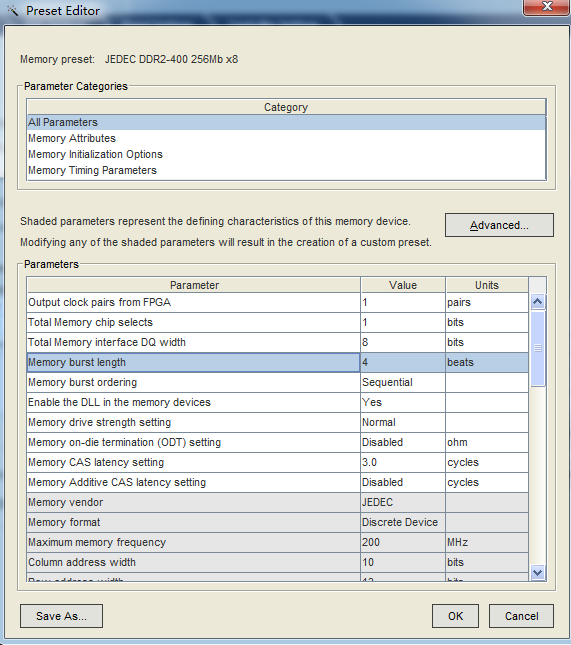

全速情况下,DDRII的突发长度为4,半速情况下,DDRII的突发长度为8。

memory preset根据自己的DDRII芯片选择,如果QUARTUS自带的设置中没有,可以自定义,选择modify parameters。

上述参数必须根据DDRII芯片手册上的参数配置。上述参数中Memory bursrt length决定的该控制器的速率模式是全速还是半速。

然后一直next,到finish,等待生成控制器文件就可以了。

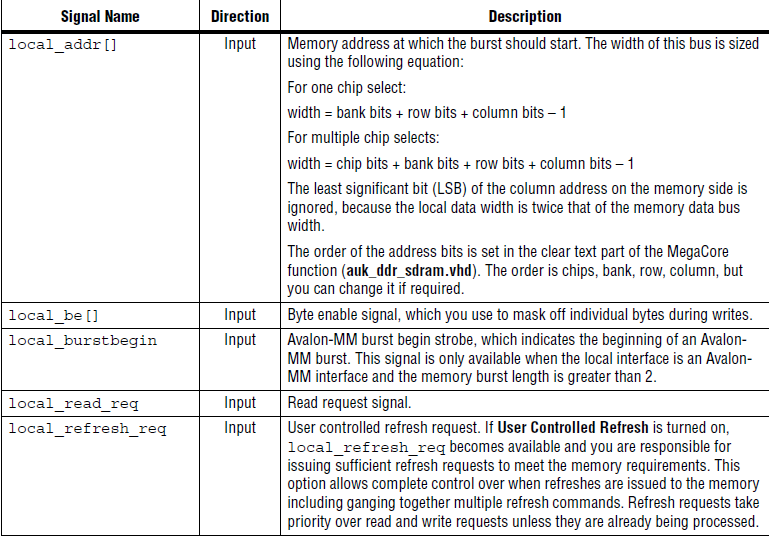

下面给出部分DDRII控制器接口。

具体端口详细说明以及读写控制时序,请参阅官方手册。

版权所有权归卿萃科技 杭州FPGA事业部,转载请注明出处

作者:杭州卿萃科技ALIFPGA

原文地址:杭州卿萃科技FPGA极客空间 微信公众号

扫描二维码关注杭州卿萃科技FPGA极客空间