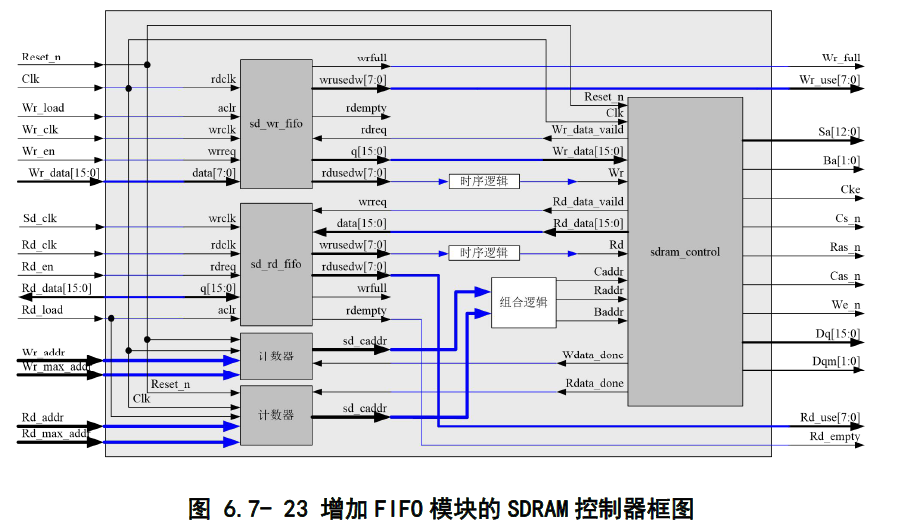

在原来控制器的基础上添加了读写FIFO,对数据进行缓存,从而解决了原控制器在某些时刻读写被忽略掉(比如刷新请求和写请求同时到来),导致数据的存储和读写出现遗漏

其中,sdram_control 模块的写使能Wr 和读使能Rd 是分别通过判断写FIFO 模块和读FIFO 模块中所存储的数据量来决定的。

在写FIFO 模块中,当存放的数据量大于一次突发写长度数据量时就将写使能Wr 拉高;

在读FIFO 模块中,当存放的数据量小于整个FIFO 能存放数据量的一半时就读使能Rd 拉高。

这样就能解决上述在连续数据流读取时,数据读取存在遗漏的问题