【转载自公众号“达尔闻说”】以Intel(Altera)的EP4CE10F17C8芯片为例:

(1)逻辑阵列块(Logic Array Block,LAB):

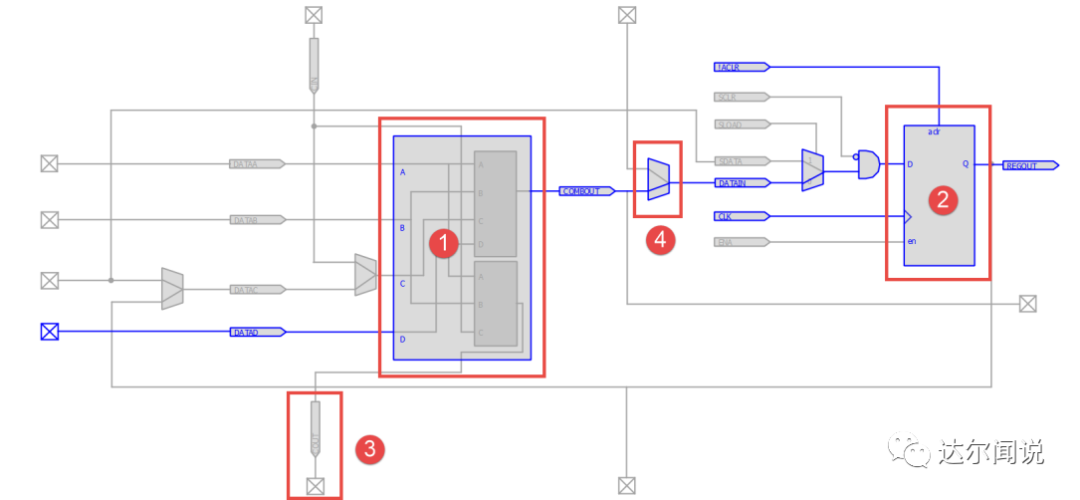

每个LAB由16个LE(Logic Element)组成,每个LE主要由左边的4输入查找表和右边的可编程寄存器组成,还包括:多路数据选择器、进位链等。查找表和多路选择器完成组合逻辑功能,寄存器完成时序逻辑功能。这里的输入查找表类似于一个容量为16 bits 的 ROM(2^4 = 16)(工艺上是珍贵的 SRAM 资源),4表示地址输入位宽为4 bits,存储的内容作为输入对应的输出结果的逻辑运算,并在 FPGA 配置时载入。

上图红色①标注处为查找表:目前主流 FPGA 都采用了基于 SRAM 工艺的查找表结构。查找表本质上就是一个 RAM。当用户通过原理图或 HDL 语言描述了一个逻辑电路以后,FPGA 开发软件会自动计算逻辑电路的所有可能结果,列成一个真值表的形式,并把真值表(即输入对应的输出逻辑)事先写入RAM,这样每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。目前FPGA中多使用4输入的查找表,所以每一个查找表可以看成一个有4位地址线的RAM。

上图红色②标注处为寄存器:可以配置成多种工作方式,比如触发器或锁存器,同步复位或异步复位、复位高有效或低有效。

上图红色③标注处为进位链:超前进位加法器,方便加法器的实现,加快复杂加法的运算。

上图红色④标注处为数据选择器:数据选择器一般在 FPGA 配置后固定下来。

(2)用户可编程I/O(User I/Os,也被简称为IOE):

可编程I/O资源分布在整个芯片的四周,一个可编程I/O单元里面又包含三个最小单元(每个可编程I/O单元中的最小单元个数不固定,有的包含两个,也有的包含四个),而最小单元内部结构又包括双向I/O缓冲器、OE寄存器、对齐寄存器、同步寄存器、DDR输出寄存器、三态门、延时模块等。

为了便于管理和适应多种电器标准,FPGA 的 IOE 被划分为若干个组(Bank),每个 Bank 的接口标准由其接口电压 VCCO 决定,一个 Bank 只能有一种 VCCO,但不同 Bank 的 VCCO 可以不同。只有相同电气标准和物理特性的端口才能连接在一起,VCCO 电压相同是接口标准的基本条件。

(3)FPGA互连线资源(Interconnect):

布线资源连通 FPGA 内部的所有单元,而连线的长度和工艺决定着信号在连线上的驱动能力和传输速度。FPGA 芯片内部有着丰富的布线资源,根据工艺、长度、宽度和分布位置的不同而划分为 4 类不同的类别:

第一类是全局布线资源,用于芯片内部全局时钟和全局复位/置位的布线;

第二类是长线资源,用于完成芯片 Bank 间的高速信号和第二全局时钟信号的布线;

第三类是短线资源,用于完成基本逻辑单元之间的逻辑互连和布线;

第四类是分布式的布线资源,用于专有时钟、复位等控制信号线。

(4)嵌入式存储单元(Memory Bits,也被称为Block RAM或简称为BRAM):

该部分资源主要用于生成RAM、ROM、FIFO以及移位寄存器等常用的存储模块,在存储较多数据或作跨时钟域处理时常用,BRAM 由一定数量固定大小的存储块构成的,使用 BRAM 资源不占用额外的逻辑资源,不过使用的时候消耗的 BRAM 资源只能是其块大小的整数倍,就算你只存了 1 bit 也要占用一个 BRAM。

相对于LUT构成的分布式RAM(Distribute RAM,简称为DRAM),这种专门的存储单元速度更快,容量更大,从而避免LUT资源的浪费,一般是 BRAM 资源不够用的情况下才使用分布式 RAM。

(5)嵌入式乘法单元(Embedded multiPlier 9-bit elements,也简称为DSP块):

该单元主要用于各种复杂的数学运算,乘法、除法以及常用的功能函数如:有限冲激响应滤波器(FIR),无限冲击响应滤波器(IIR),快速傅里叶变换(FFT),离散余弦变换(DCT)等,这些功能函数在运算时会消耗很多逻辑资源,而FPGA中的LUT和寄存器资源有限,这时候使用嵌入式乘法单元这部分资源就不会造成逻辑资源的浪费。

(6)锁相环(Phase Lock Loop,PLL):

锁相环路是一种反馈控制电路,简称锁相环。锁相环的特点是利用外部输入的参考信号控制环路内部振荡信号的频率和相位。因锁相环可以实现输出信号频率对输入信号频率的自动跟踪,所以锁相环通常用于闭环跟踪电路。锁相环在工作的过程中,当输出信号的频率与输入信号的频率相等时,输出电压与输入电压保持固定的相位差值,即输出电压与输入电压的相位被锁住,这就是锁相环名称的由来。

PLL的参考时钟输入都是由专用时钟管脚上的晶振进来的,用于时钟的倍频、分频,以及相位、占空比调制。PLL出来的时钟都会连接到全局时钟网络上,如下图所示就是通过全局时钟网络扇出到每个寄存器上的时钟线,全局时钟网络保证时钟的质量,减小时钟偏斜(Skew)和抖动(Jitter)。

不同厂家不同系列的FPGA芯片其内部资源会稍有差异,但都会包含以上这些主要的内部资源。