intest scan的一些基本知识。

INTEST scan指的是对IP 内部的scan cell的扫描测试,针对IP内部的flip-flop进行shift/capture的操作。

和INTEST SCAN 对应的就是EXTEST SCAN, 顾名思义,所指的也就是IP之间的glue logic的SCAN CELL 的测试。这部分SCAN CELL 包括了IP之间的flip-flop以及IP的input的第一级flip-flop,这主要是因为,IP的第一级flip-flop再做INTEST测试的时候只能用于shift data,并不能进行capture,所以需要在EXTEST的时候进行测试。

下图所示,就是一个IP的INTEST的data flow。

每个IP有对应的scan_in,scan_out channel,它们的channel的数量是由每个IP内部的scan_cell数量,EDT的压缩比,以及short chain的数量决定的。

1. 根据Mentor的工具建议来看,一个short chain上面的scan_cell数量可以在250~300之间。

2. 每个IP每部的压缩比的尽量在100~150条之间,如果压缩比过大,可能导致的问题是compressor/decompressor的内部logic过大,会插入比较多的pipeline。从而导致整条scan chain的长度变得很大。

在计算scan_in/out 和内部的short chain数量的时候,会经过多次迭代,每次根据生成的EDT模块,来看压缩比否合适,尽量保持EDT内部的pipeline长度小于short chain的 1/5.

为什么会分为intest和extest两种测试模式呢?

原因其实还是在于做scan时候的无法测到IP之间的gule logic。

首先来看一下SOC的整体结构,再做scan的时候,我们会划分为ip leve和soc level。

ip level就是指测试ip内部的所有scan cell,通过shift->capture->shift这个过程,将内部所有的flop进行检查,主要是检查flop通路,以及logical path是否存在stuck at fault,以及测试signal transition能否满足timing。这些问题可以通过DC/AC mode来进行检查。关于DC/AC mode,后面会有一篇文章专门讲解。

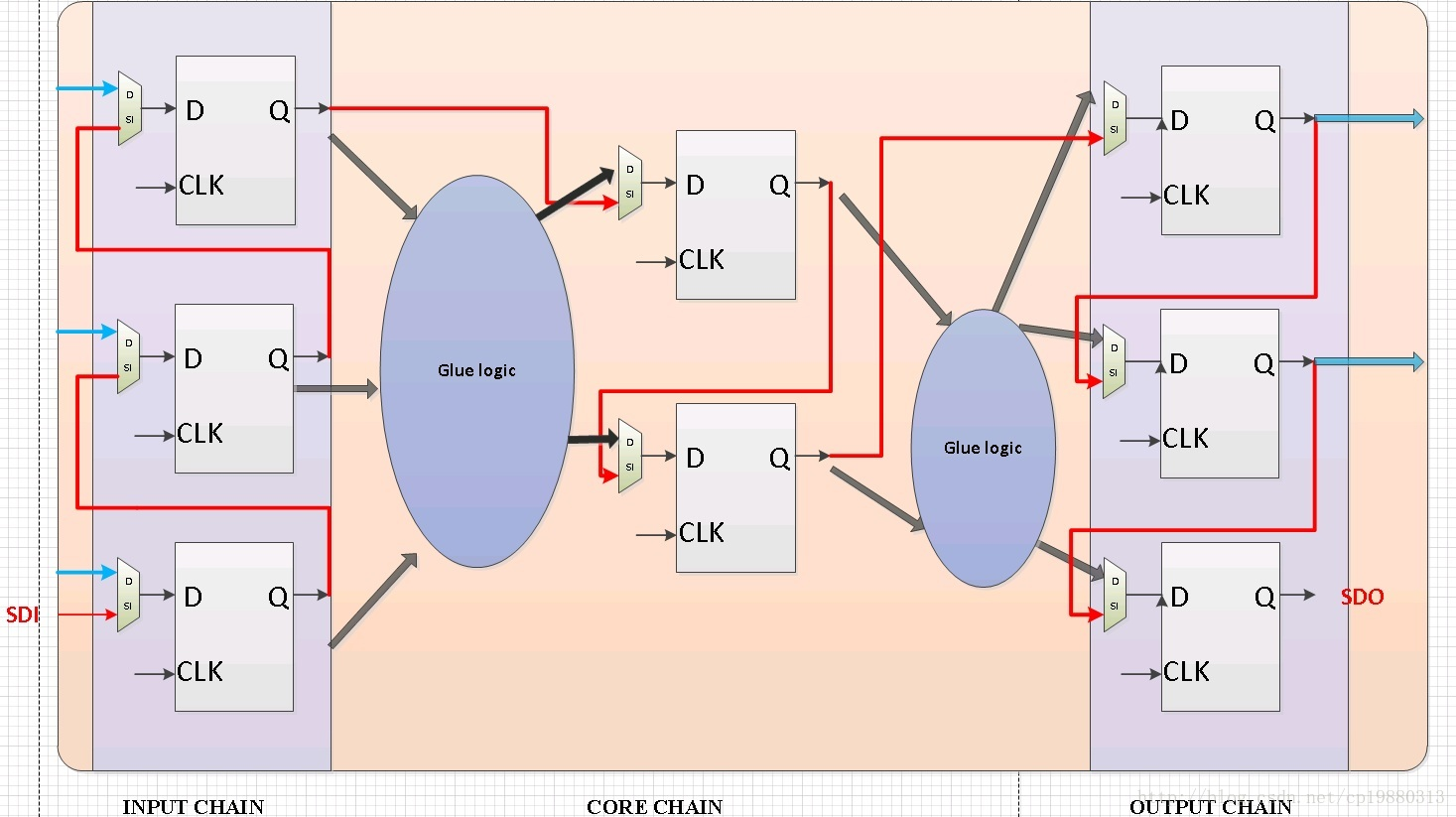

这张图画出了IP level intest的结构,红色的线代表的是scan data input/output,蓝色的线代表function data input/output。

当进行scan的时候:

1. SE =1, SDI shift data 8 cycle,将所有的flop的D pin都已经给到一个data。

2. SE = 0, clock切换到function clock,进入capture mode,此时用fuction clock shift 1 cycle,将D pin数据输出到下一个flop的D pin上。

3. SE = 1, clock切回shift clock,进入到shift mode,将flop的数据逐个SHIFT 出来,输出到SDO,在ATE上完成一组vector的测试。

看起来整个流程是可以的,但在整个流程上,第一级的flop,也就是途中input chain中的紫色三个flop实际上是没有办法测到正常的capture模式,因为在capture mode情况下,INPUT CHAIN的SE始终要保持为1(也就是第一级的flop一直要选择红儿箭头的输入),如图蓝色的箭头所示,蓝色箭头是外部给过来的function input,在IP level,是没有办法控制它们的input,所以在capture mode下,SE =1,此时capture出来的数据实际上就是shift进来的scan input data。

在这种情况下,IP之间的glue logic没有办法验证到。

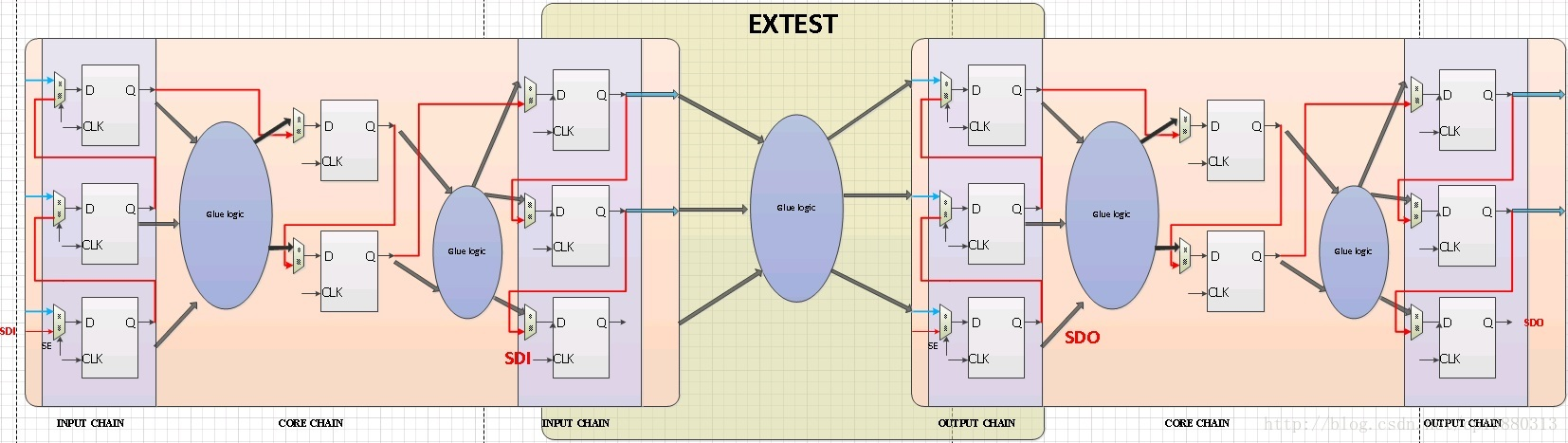

如下图所示,当两个IP之间的glue logic需要进行测试的时候,此时,第一个IP的最后一级flop就变成了INPUT CHAIN, 而第二个IP的第一级flop就变成了OUTPUT CHAIN.

此时也就形成了一个IP之间的SCAN test,这样也就可以完全测试到capture mode下的flop以及logic部分。