随机访问存储器(Random Access Memory,RAM)

RAM分为两种:静态的和动态的。

SRAM,用来作为高速缓存存储器,既可以放在CPU芯片上,也可以放在片下。由于SRAM存储器单元的双稳态特性,只要有电,它就会永远地保持它的值。即使有干扰来扰乱电压,当干扰消除时,电路就会恢复到稳定值。

DRAM,用来作为主存以及图形系统的帧缓冲区。DRAM将每一个位存储为对一个电容的充电。当电容的电压被扰乱后,它就永远不会恢复了。

传统的DRAM

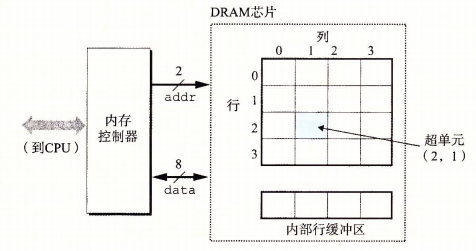

DRAM由若干个DRAM芯片组成,每个DRAM芯片被分成d个超单元,每个超单元中存放w位。一个d×w的DRAM总共存储dw位信息。

下面是一个16×8的DRAM芯片的高级视图:

DRAM中的超单元被组织成一个r行c列的矩阵,rc=d。

信息通过被称为引脚(pin)的外部连结器流入和流出芯片。每个引脚携带一个位的信息。

每个DRAM芯片被连接到某个称为内存控制器的电路,这个电路可以一次传送w位到每个DRAM芯片或一次从每个DRAM芯片传出w位。

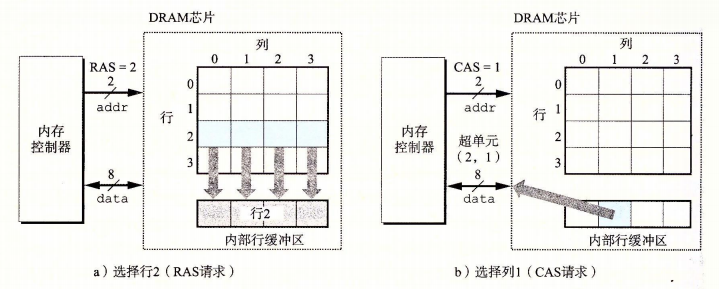

为了读取超单元(i,j)中的内容,内存控制器将行地址 i (RAS)发送到DRAM,然后是列地址 j (CAS)。RAS和CAS共享同一个DRAM地址引脚。所以每次访问超单元都需要将行地址和列地址分两次传输。

下面是一个超单元的读取流程:

由DRAM芯片组成的内存模块

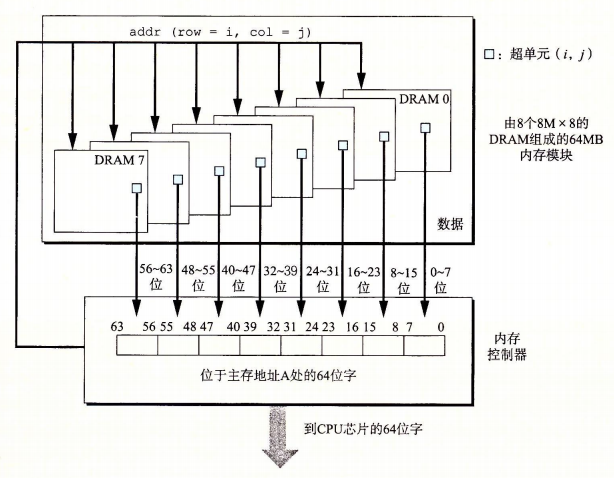

下面是一个用8块DRAM芯片组成的内存模块的示意图:

其中DRAM 0存储第一个字节(低位),DRAM 7存储最后一个字节。

要取出内存地址A处的一个字,内存控制器将A转换成一个超单元地址(i,j),并将它发送到内存模块,然后内存模块再将 i 和 j 广播到每个DRAM芯片中。作为响应,每个DRAM芯片输出其(i,j)超单元的8位内容。模块中的电路收集这些输出,并把它们合并成一个64位的字,再返回到内存控制器。

非易失性存储器

所谓易失的,就是说如果断电,存储器会丢失它们的信息。另一方面,非易失性存储器即使是在关电后仍然保存着它们的信息。

这种类型的存储器都被称为只读存储器(Read-Only Memory,ROM),尽管ROM中有些类型既可以读也可以写。

PROM,可编程ROM,只能被编写一次。

EPPROM,可擦写可编程ROM,可以擦出重写。主要借助于一个独立的光学设备。

EEPROM,电子可擦除ROM,类似于EPPROM,但它不需要一个独立的物理设备。闪存就是一种基于EEPROM的存储设备。

CPU与主存的数据交换方式

数据通过称为总线的共享电子电路在处理器和DRAM主存之间来来回回。

总线是一组并行的导线,能携带地址、数据和信号。

系统总线连接CPU和I/O桥接器,I/O桥接器是一组芯片结构,其中就包括内存控制器。它的功能除了内存控制器外,还将系统总线的电子信号翻译成内存总线的电子信号。

内存总线连接I/O桥接器和主存。

磁盘存储

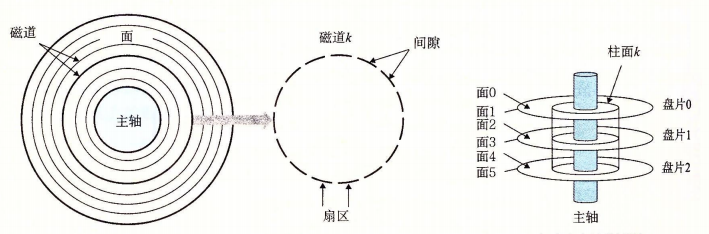

下面给出一个磁盘的结构示意图:

寻址顺序:磁盘→盘片→面→磁道→扇区→字节

所以一个磁盘的容量大小为:

磁盘容量=(每扇区的字节数)*(每磁道的扇区数)*(每面的磁道数)*(每盘片的面数)*盘片数

通常一个盘片有两个面。

磁盘的访问时间

磁盘的访问时间分为三个部分:

寻道时间:为了读取某个目标扇区的内容,传动臂首先将读写头定位到包含目标扇区的磁道上。移动传动臂的时间称为寻道时间。

旋转时间:定位了磁道后,旋转磁片到需要的扇区,这段时间称为旋转时间。

传送时间:读写数据的时间。

一次平均的磁盘访问时间=Tavg seek + Tavg rotation + Tavg transfer = Tavg seek + 30/RPM + 60/RPM * 1/(每磁道的扇区数)

固态硬盘(Solid State Disk,SSD)

固态硬盘是一种基于闪存的存储技术,在某些情况下是磁盘的替代产品。

固态硬盘的一个典型的特征就是:读比写快。

随机写很慢,原因有两个:首先擦出块需要相对较长的时间,比访问页所需时间要高出一个数量级。其次,如果写操作试图修改一个包含已经有数据的页,那么这个块中所有带有有用数据的页都必须复制到一个新的块中。

局部性(Locality)

局部性:倾向于引用邻近于其他最近用过的数据项的数据项,或者最近引用过的数据本身。这种倾向性,被称为局部性原理,对硬件和软件系统的设计和性能都有着极大的影响。有良好局部性的程序比局部性差的程序运行的更快。

时间局部性:在一个具有良好时间局部性的程序中,被引用过一次的内存位置很可能在不远的将来再被多次引用。

空间局部性:在一个具有良好空间局部性的程序中,如果一个内存位置被引用了一次,那么程序很可能在不远的将来引用附近的一个内存位置。

量化评价局部性的一些简单原则:

- 重复引用相同变量的程序由良好的时间局部性。

- 对于具有步长为k的引用模式的程序,步长越小,空间局部性越好。具有步长为1的引用模式的程序有很好的空间局部性。在内存中以大步长跳来跳去的程序空间局部性会很差。

- 对于取指令来说,循环有好的时间和空间局部性。循环体越小,循环迭代次数越多,局部性越好。

高速缓存的访问原理

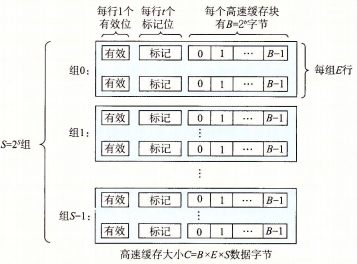

下图是一个高速缓存的结构图:

高速缓存是一个高速缓存数组。每个组包含一个或多个行,每个行包含一个有效位(有效位用于标记这一行是否有效,即这一行中是否存放数据项),一些标记位,以及一个数据块,而每个数据块中又包含多个字节(寻址的最小单位就是字节)。

一般而言,高速缓存的结构可以用元组(S,E,B,m)来描述。高速缓存的大小(或容量)C指的是所有块的大小的和。标记位和有效位不包括在内。因此C=S×E×B。

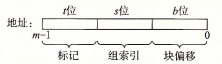

下图是一个m为的地址:

一个 m 位的地址被分成 t 位的标记位,s 位的组索引和b 位的块偏移位。

组索引位用于在高速缓存数组中确定组号,标记位用于在一个确定的组中确定行号,块偏移用于在一个确定的行中确定最终需要的字节。