在FPGA设计中常遇到复位的设计,一般情况下,复位分为同步复位和异步复位。

异步复位与同步复位相比,其利用到了D触发器的CLR端,消耗硬件资源小,所以在很多情况下各个模块的复位方式选取为异步复位。但是异步信号容易产生潜在的危险:当异步复位信号在时钟上升沿附近取消复位状态时,时序电路很可能在此出现问题。

解决这个问题的一个方法为,对异步复位信号进行预处理,使其成为异步复位、同步释放的形式。

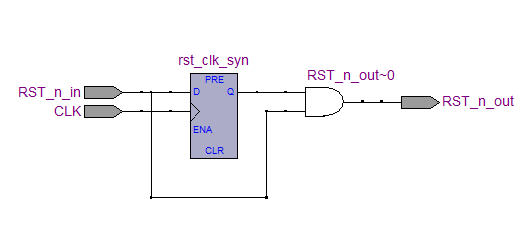

我设计的电路如下:

library ieee; use ieee.std_logic_1164.all; use ieee.std_logic_unsigned.all; entity Reset is port( CLK: in std_logic; RST_n_in: in std_logic; RST_n_out: buffer std_logic ); end Reset; architecture ex of Reset is signal rst_clk_syn: std_logic; begin RST_n_out <= rst_clk_syn and RST_n_in; process(CLK, RST_n_in) begin if(CLK'event and CLK = '1') then rst_clk_syn <= RST_n_in; end if; end process; end ex;

其RTL级综合结果如下:

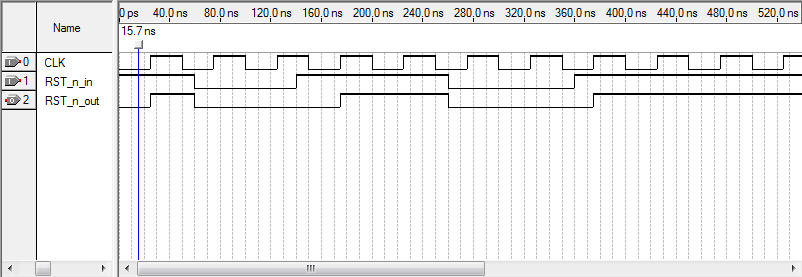

其功能仿真结果如下:

异步复位信号经过这个结构后,再传到其他异步复位模块,便可以减少异步信号造成的不稳定现象。