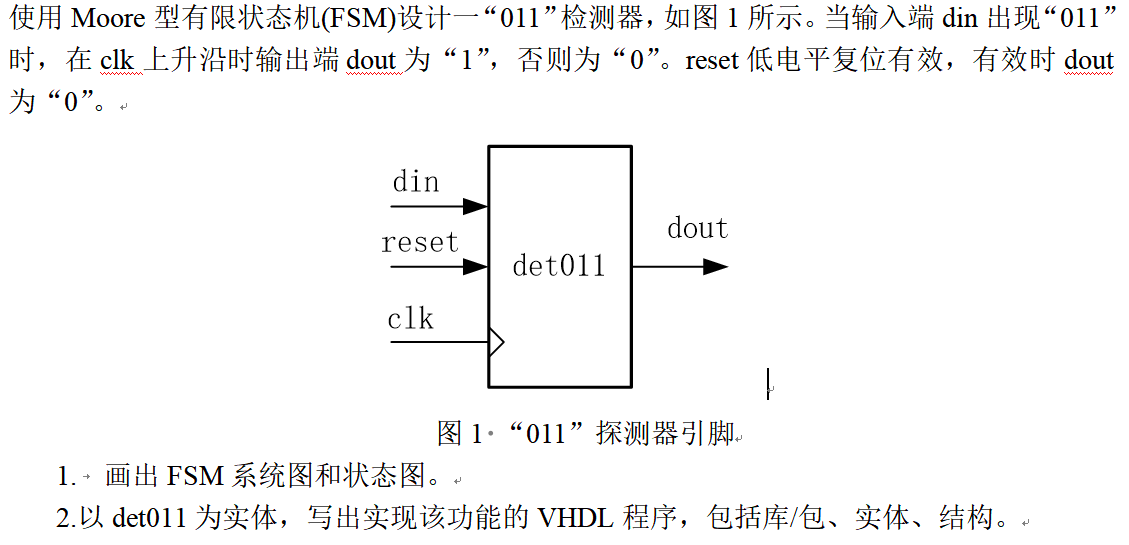

【题目描述】

【分析】

题意:对于该题分析一下“011”检测器,我最开始的时候以为din输入的是vector,后来发现原来是连续输入的信号,序列“011”时输出为“1”

reset低电平有效:指的是reset在低电平时进行复位,所以需要这样写;

为什么用Moore型的状态机呢?

因为最开始理解题目为输入为向量,所以就会有这样的想法。

其实输入不能直接影响其输出,哪怕是输入直接为“011”的向量形式,其状态改变都是等待时钟为上升沿,其对应状态才能输出。所以说是间接影响输出,但din仅仅是影响状态的改变,而输出却仅仅看状态形式。典型的Moore型状态机。

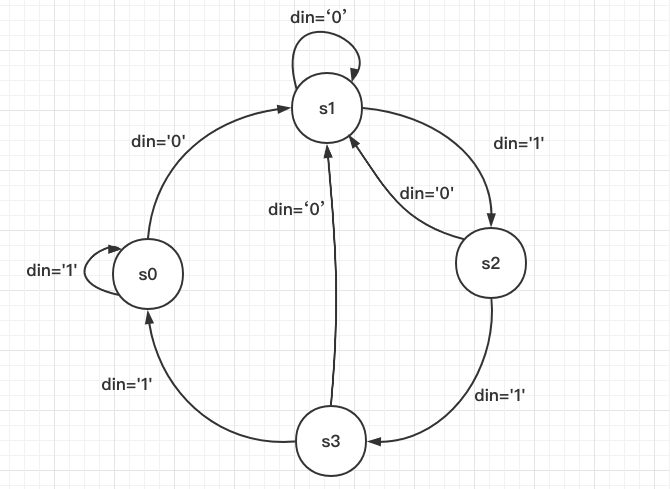

设计其状态图

分析,其实所有‘0’都可能是最开始输入的“011”中的首位。所以任何状态在din为0时都对应转化,其余的对应一一转化即可。

因为是异步复位,还需要多增设S0状态来表示。

【状态图】

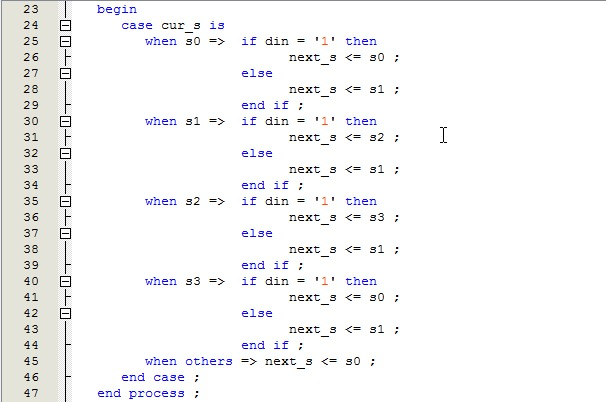

【代码】

1 library ieee; 2 use ieee.std_logic_1164.all ; 3 4 entity det011 is 5 port ( clk , din , reset : in std_logic ; 6 dout : out std_logic ); 7 end entity ; 8 9 architecture behave of det011 is 10 type state is ( s0 , s1 , s2 , s3 ) ; 11 signal cur_s , next_s : state ; 12 begin 13 main_process : process ( clk , reset ) 14 begin 15 if reset = '0' then 16 cur_s <= s0 ; 17 elsif clk'event and clk = '1' then 18 cur_s <= next_s ; 19 end if; 20 end process ; 21 22 state_trans : process ( cur_s , din ) 23 begin 24 case cur_s is 25 when s0 => if din = '1' then 26 next_s <= s0 ; 27 else 28 next_s <= s1 ; 29 end if ; 30 when s1 => if din = '1' then 31 next_s <= s2 ; 32 else 33 next_s <= s1 ; 34 end if ; 35 when s2 => if din = '1' then 36 next_s <= s3 ; 37 else 38 next_s <= s1 ; 39 end if ; 40 when s3 => if din = '1' then 41 next_s <= s0 ; 42 else 43 next_s <= s1 ; 44 end if ; 45 when others => next_s <= s0 ; 46 end case ; 47 end process ; 48 49 output_process : process ( cur_s ) 50 begin 51 case cur_s is 52 when s3 => dout <= '1' ; 53 when others => dout <= '0' ; 54 end case ; 55 end process ; 56 end behave ; 57 58 59 60 61 62 63 64 65 66 67

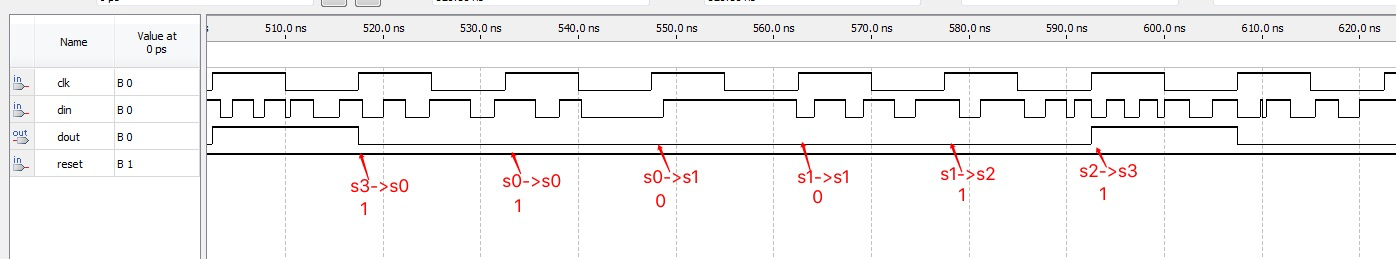

【波形图分析】

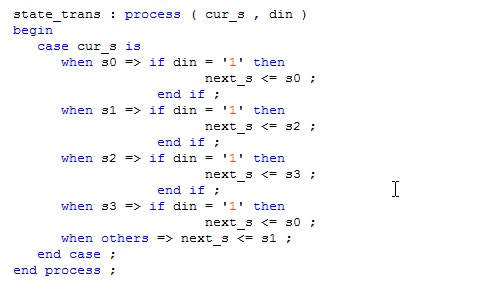

【注意事项】

在写状态变化时,请每条边都一一对应,然后其余的情况都归S0(初始态)。

如果写成对应程序就会dout一直为‘0’

错误写法↑

正确写法↑