Verilog 读写文件

在数字设计验证中,有时我们需要大量的数据,这时可以通过文件输入,有时我们需要保存数据,可以通过写文件保存。

读写文件testbench

module file_rw_tb();

reg clk;

reg rstn;

reg [31:0] memh[15:0];

reg [31:0] data;

integer i;

integer handle;

initial

begin

clk = 0;

rstn = 1;

#50 rstn = 0;

#100 rstn = 1;

handle=$fopen("wtest.dat");

//read data to memory

$readmemh("test.dat",memh);

//write data to file

for(i=0;i<16;i = i + 1)

begin

$fdisplay(handle,"%h",memh[i]);

//%b Binary ; %h Hexadecimal ; default decimal

end

#800 $finish;

end

always #20 clk = ~clk;

initial begin

$fsdbDumpfile("test.fsdb");

$fsdbDumpvars();

end

endmodule

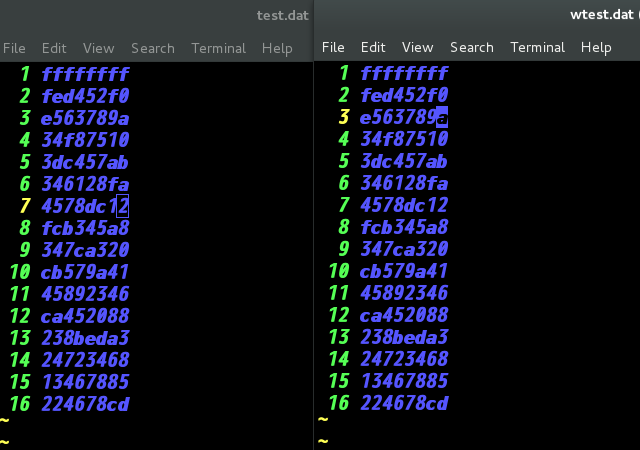

测试结果