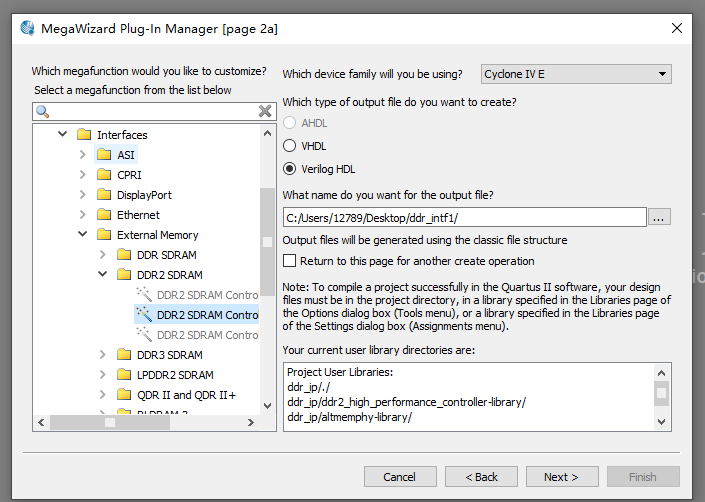

打开IP核工具,然后选择Verilog HDL选项,填写路径,写入文件名DDR2_IP.V,点击next

PLL reference clock frequency填入板子晶振的频率50MHZ,这里设置Memory clock frequency为133MHZ,Controller data rate 为Full模式。

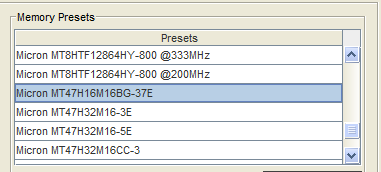

芯片型号如果有相同的就选相同的,如果没有就选类似的,然后修改参数。这里选择

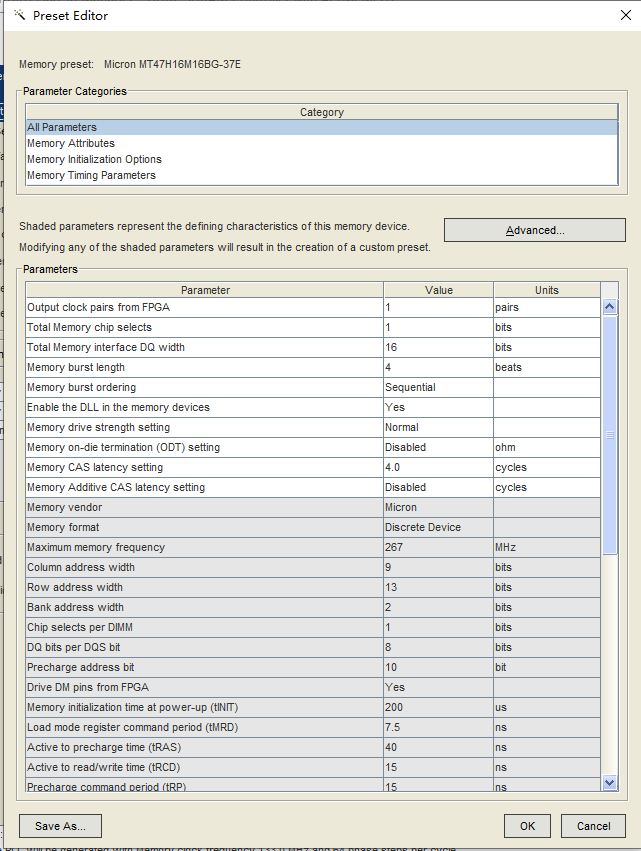

然后点击Modify parameters设置参数,也可以选择Loda Preset载入设置好的参数

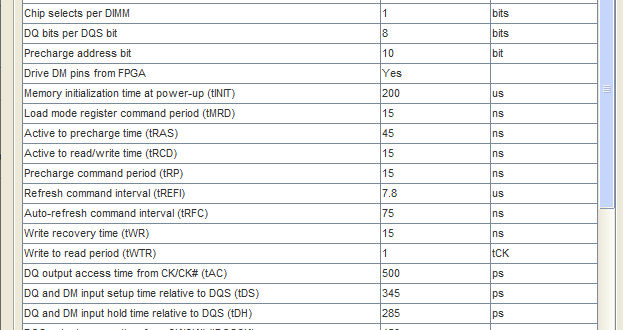

根据芯片手册设置参数,我这里使用的是MT47H16M16BG-3 IT-B TR修改三个参数就好了

修改完毕,点击OK,然后,NEXT

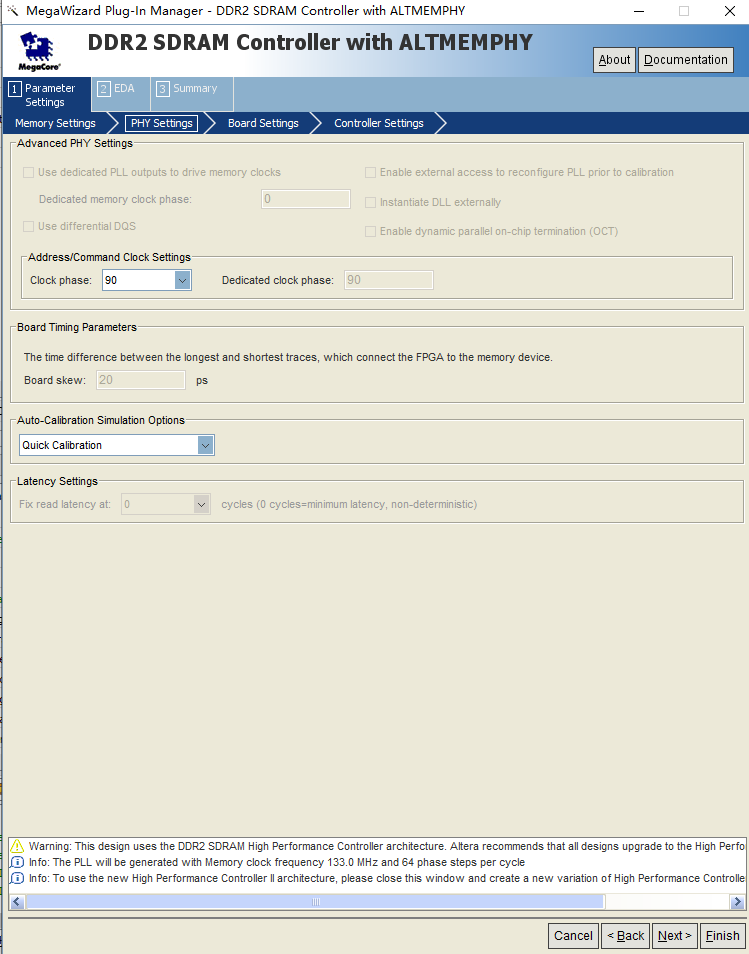

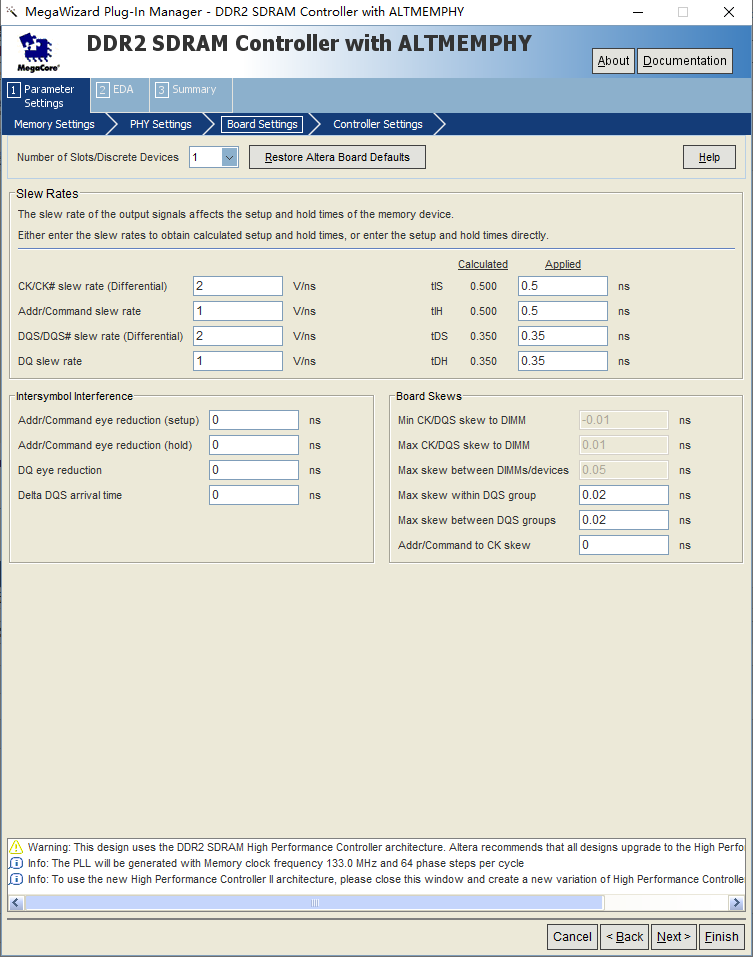

NEXT

next

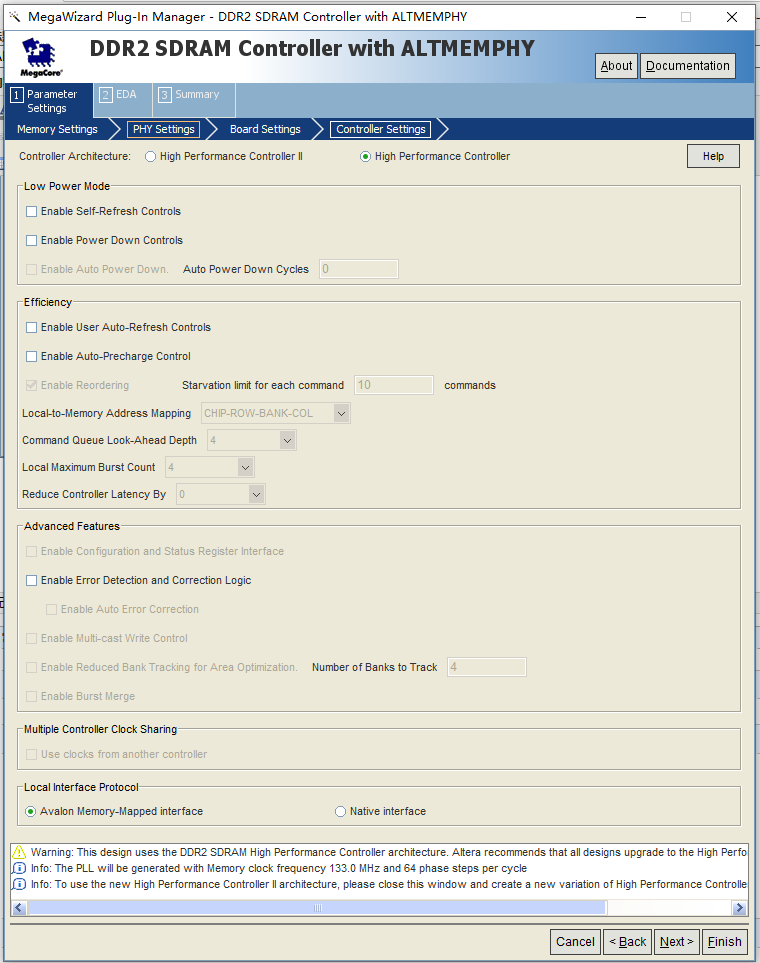

这里选择一代,忽视警告,NEXT

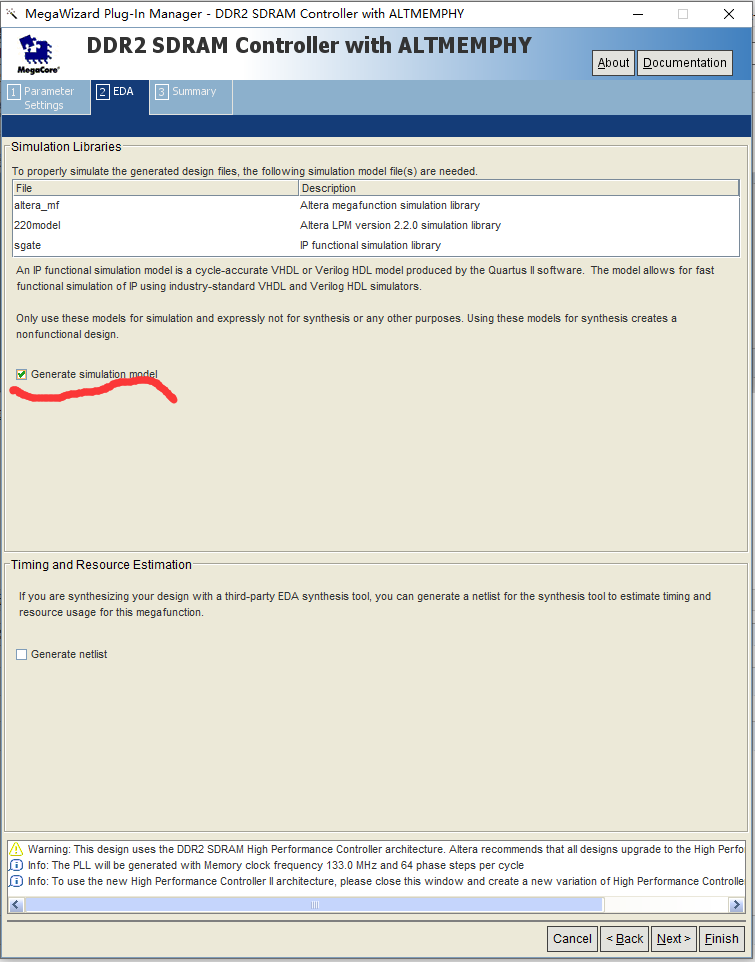

这里打钩,然后NEXT

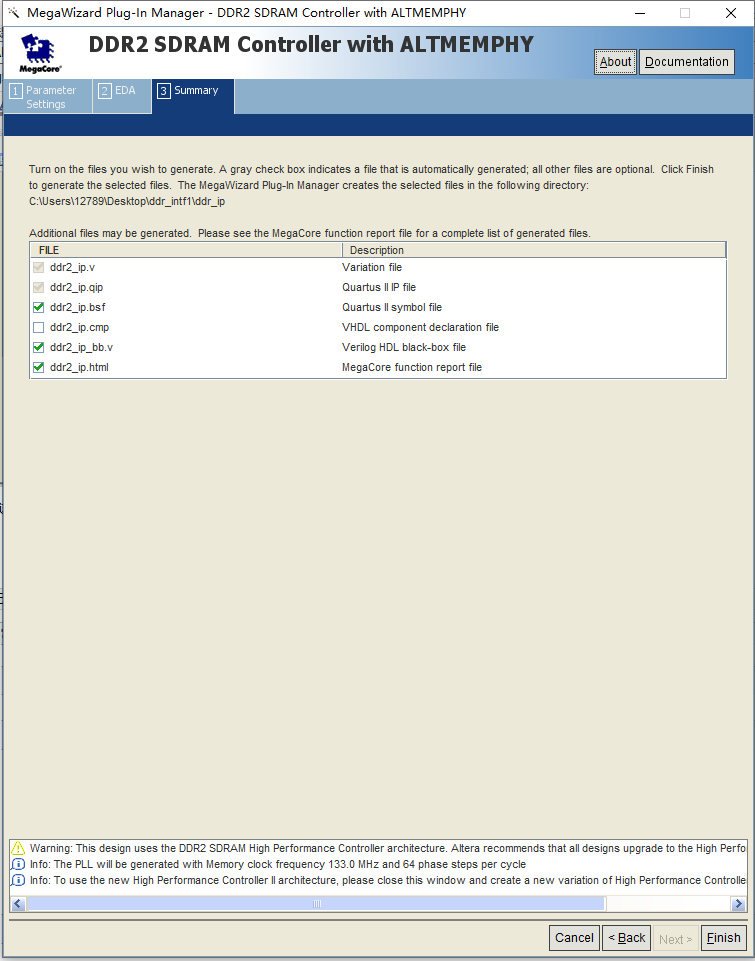

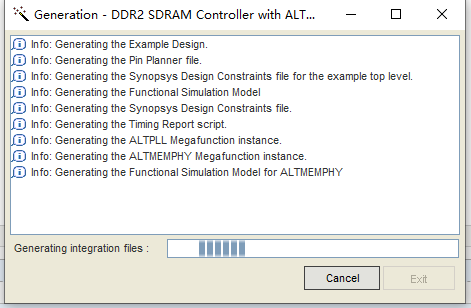

点击Finish,等待IP核生成。

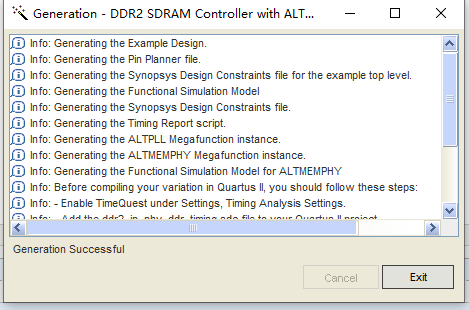

等待生成完成,点击EXIT。

IP核生成完毕,IP核的生成本身没有什么讲究,初学阶段,不要过分纠结参数的意义,跟着做,先跑完整个流程,可以仿真,可以用,

然后再从整体到局部,这样的学习比较有效率。否则学得特别慢,而且容易卡在某个点上。