SRAM,DRAM,SDRAM和DDR2这些芯片详解网上铺天盖地的各种资料都有,这里只是根据个人习惯做一下总结,方便记忆。

详细资料可以参考https://wenku.baidu.com/view/36eb2521af45b307e8719786.html?sxts=1560173120906

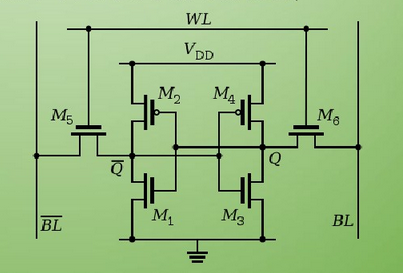

SRAM基本存储单元结构

SRAM中的每一bit存储在由四个场效应管(M1-M4)构成的两个交叉耦合的反相器中,另外两个场效应管(M5,M6)是存储基本单元

到用于读写的位线(Bit Line)的控制开关。

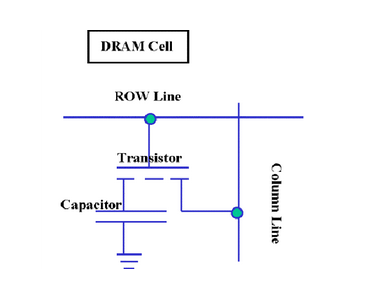

DRAM基本存储单元结构

DRAM的每一个Bit都由一个MOS管和一个电容组成,通过ROW LINE也就是MOS管的栅极来控制电容跟Column Line的导通与关闭,

通过Column Line来读取电容的高低电平。

优缺点比较:

地址总线差异:SRAM分为单地址总线,DRAM为双地址总线(行地址,列地址)原因是因为存储1bit的数据SRAM需要4-6个晶体管,

但是DRAM仅仅需要1个晶体管,这样相同容量的SRAM的体积比DRAM大至少四倍。这意味着DRAM没有足够的空间安放同样数量的引脚

(因为针脚并没有因此减少4倍)。如果为了安装同样数量的针脚而把DRAM芯片的体积加大,就会提高芯片的生产成本和功耗,所以减少

针脚数目也是必要的。对于现在的大容量DRAM芯片,多路寻址技术已经是必不可少的了。

读写速率差异:SRAM可以运行在比DRAM更高的频率,SRAM需要2-3个时钟周期来获得想要的数据(这里我们暂时忽略CPU,芯片组核内存DIMM

控制电路之间的延迟),同样的过程DRAM需要大约3-9个时钟周期。原因是因为DRAM采用一个晶体管和一个电容组成,这样的组成虽然是目前

最经济的方式,但是电容储存的电荷实惠慢慢泄露的,为了保证内存中数据的正确性需要不时的刷新内存,电容需要电流进行充电,而电流充电的

过程是需要一定时间的,一般是0.2-0.18微秒(由于内存工作环境所限制,不可能无限制的提高电流的强度),在这个充电的过程中内存是不能被访问的,

这就意味着DRAM基本存储单元大约有1%的时间用在刷新上。同事读取内存会导致内存基本存储单元中的电荷丢失,所以每当DRAM被访问之后都要进行

刷新,以维持访问之前的状态,否则就会导致数据丢失。因为SRAM不存在刷新问题,SRAM采用了4个晶体管核两个电阻器构成的结构,它并不利用电容器

来存储数据,而是通过切换晶体管的状态来实现,所以读取的过程中不会造成SRAM内存数据的丢失。

综上所述两种芯片速率,成本,容量差异较大,所以两者都有自己更适合的场所。