系统基本构成

- 处理器

- 内存

- 输入/输出模块

- 系统总线

处理器的寄存器

用户可见寄存器

- 数据寄存器,包括一些通用寄存器、与浮点专用寄存器

- 地址寄存器:

* 变址寄存器

* 段指针

* 栈指针

控制和状态寄存器

- 程序计数器PC:即将取指令的地址

- 指令寄存器IR:最近取得指令内容

- 程序状态字PSW:包含状态信息,如中断允许/禁止位、内核/用户态位

- 中断寄存器:指向中断处理程序

指令的执行

指令周期:取出一条指令并执行这条指令的时间,分为取指阶段和执行阶段

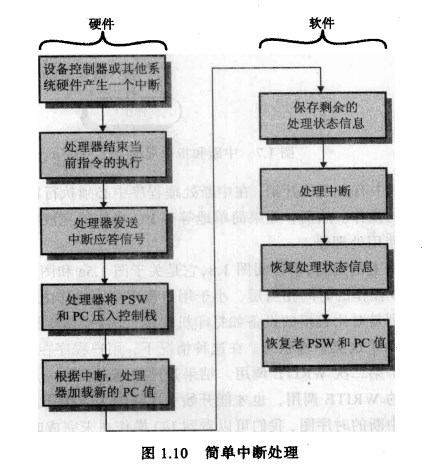

中断

允许其他模块(I/O、存储器)中断处理器正常处理过程的机制。

中断分类

| 种类 | 说明 |

|---|---|

| 程序中断 | 某些条件下执行指令产生,如算数溢出、除数为0、试图执行非法指令、访问不允许的储器位置 |

| 时钟中断 | 处理器内部计时器产生,允许操作系统以一定规律执行函数 |

| I/O中断 | I/O控制器产生,用于发送信号通知操作正常完成或发生错误 |

| 硬件失效中断 | 如掉电、存储器奇偶校验错误 |

中断与指令周期间关系

- 中断处理

- 多个中断的处理

- 处理多个中断方法1、当正在处理一个中断时,禁止再发生中断,处理完毕后允许中断。

- 处理多个中断方法2、定义中断优先级,允许高优先级中断打断低优先级中断处理程序的运行。

存储器的层次结构

分层是容量、存取时间、价格三者的折中。从上到下,存取时间递增、单位价格与容量递增、访问频率递减。

高速缓存

高速缓存用于在内存和处理器的寄存器之间分段移动数据,以提高数据访问性能。由于局部性现象的存在,很可能紧接着的多次访问的数据是块中的其他字节。

替换高速缓存中的块的策略为LRU。在块被替换出缓存之前,被修改的块将会被写回内存。

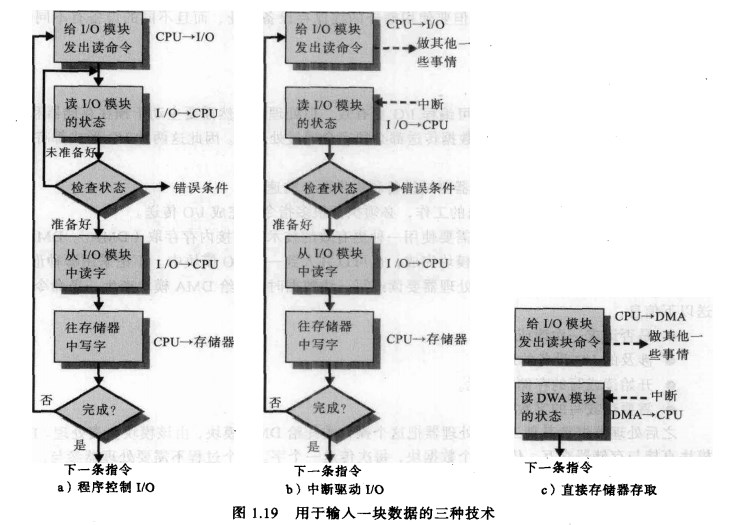

I/O通信技术

- 可编程I/O

- 中断驱动I/O

- 直接内存存取

使用直接内存存取DMA方式时,DMA模块直接与存储器交互,传输完成后DMA模块会给CPU发一个中断信号。CPU只有在开始传输与结束传输时才会参与。

当处理器要读或写一块数据时,它给DMA模块命令,告诉它

- 读或写

- 涉及的I/O设备的地址

- 开始读或写的存储单元

- 需要读或写的字节大小

附录A 局部性

局部性原理的有效性在于

- 除分支和调用指令外,程序是顺序执行的,且分支和调用只占了执行语句中的一小部分

- 调用时,在较短时间内,指令的引用局限在很少几个过程中

- 循环时,计算被限制在一个很小的相邻部分中

- 很多计算涉及连续内存的数据结构,大多数情况下,对这类数据结构的连续引用是对相邻的数据项进行操作的

局部性分为

- 空间局部性

- 时间局部性

附录B 过程控制

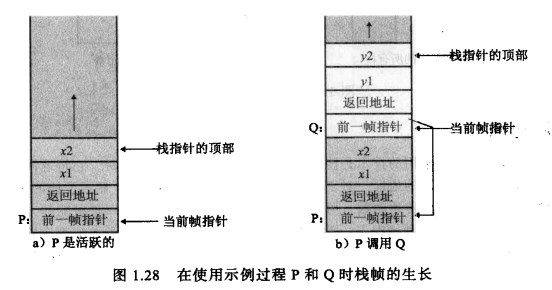

过程调用与返回

管理过程调用与返回的最常用技术是使用栈,大多数机器中,栈是从高地址向低地址增长的。

执行一次调用时,会在栈中保存返回地址与传递给被调用过程的参数。被调用过程中从栈中访问这些参数,在返回之前,返回参数可以放在栈中返回地址的下面。为一次过程调用保存的整合参数集合,包括返回地址,称作栈帧(stack frame)。

每个栈帧的第一项是一个指针,指向前一帧的首地址。如果参数的数量与长度是可变的,就会用到该地址。

可重入过程

可重入过程是指程序代码的一个副本在同一段时间内可以被多个用户共享使用。

两个重要特征:

- 程序代码不能修改其自身、每个用户的局部数据必须单独保存。

- 一个可重入过程可以被中断,由一个正在中断的程序调用,在返回该过程时仍能正确执行。

简单的说,就是要么没状态,要么状态是局部的,不共享的。