26.核心初始化之关闭MMU和cache

下面看看ARM存储体系:

可以看到速度最快的是处理器和内部寄存器,他们的数量很少,价格很昂贵。接着是TCM紧耦合存储器:cache和main memory。速度最慢的是外部存储介质:Flash和SD卡等。

CACHE:

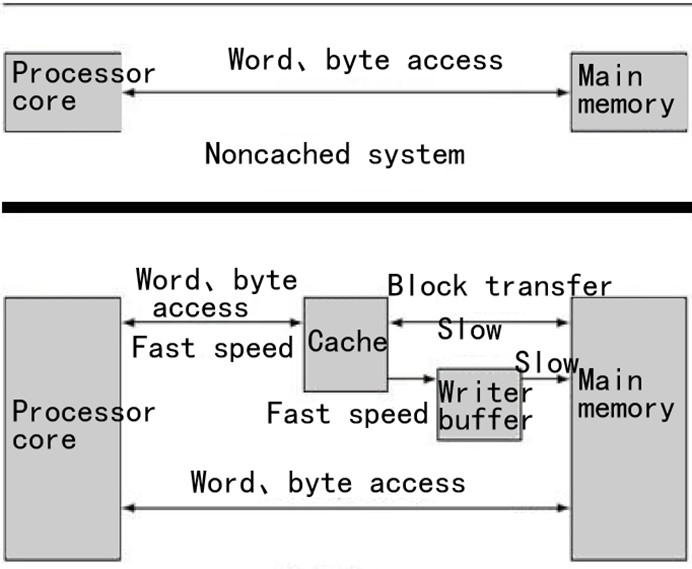

上面是两种访存的两种机制,一种是处理器直接访问主存,另一种是处理器-cache-主存。第一种中,处理器的速度相比主存是非常快的,所以两者的速度很不匹配。浪费了处理器的很多资源。第二种是为了改进第一种的缺陷,在处理器和主存之间增加了一种叫Cache的原件,cache的访问速度比主存快,比处理器慢了点,这样就缓和了第一种的资源浪费现象。

其实在cache里存放的是主存的一些数据的拷贝:当处理器要访问主存里的数据的时候,处理器会先到cache里面找,如果里面没有想要的数据,再到主存里面访问,此时主存除了把数据总到处理器之外,他还拷贝一份数据到cache里。下一次处理器访问数据的时候,还是到cache里面找,如果有就直接取走。不用访问主存。有人做过统计,就是处理器会频繁使用某些数据,有些数据处理器很久才使用一次。这样就大大地提高了访问的速度了。

Cache是一种容量小但存取速度非常快的存储器,它保存最近用到的存储器中数据的拷贝。对于程序员来说,Cache是透明的。它自动决定保存哪些数据、覆盖哪些数据。按照功能划分:

I-Cache: 指令Cache,用于存放指令

D-Cache:数据Cache,用于存放数据

2440的I/D-cache:

6410:

210:

虚拟内存:

假如一个程序员,编写了三个程序,都需要访问内存。而且操作系统中还有其他的应用程序。然而作为程序员,都是表层操作的,程序员都只是懂得软件的编写。他们怎么知道哪些物理地址被用了呢?他要使用哪些物理地址才不会冲突呢?最后很可能是两个应用程序访问同一个物理内存,就会产生地址冲突。还有就是实际的物理地址范围是很有限的。

但是引入了虚拟地址之后,程序员应用程序员不需要知道哪些物理地址被使用,因为他们使用的是虚拟地址。即使三个应用程序使用了同一个虚拟地址,最后系统会把这三个虚拟地址映射到不同的物理地址去执行。这样就不会产生冲突了。这样程序员使用的虚拟地址的范围比物理地址大了很多。

虚拟地址:程序使用的地址

物理地址:物理存储单元实际的地址

虚拟地址:

-

可以让进程使用更大的空间

-

可以解决冲突

那么谁来实现虚拟内存到物理内存的转换呢?这就是下面的MMU解决的问题了。

MMU的机制:

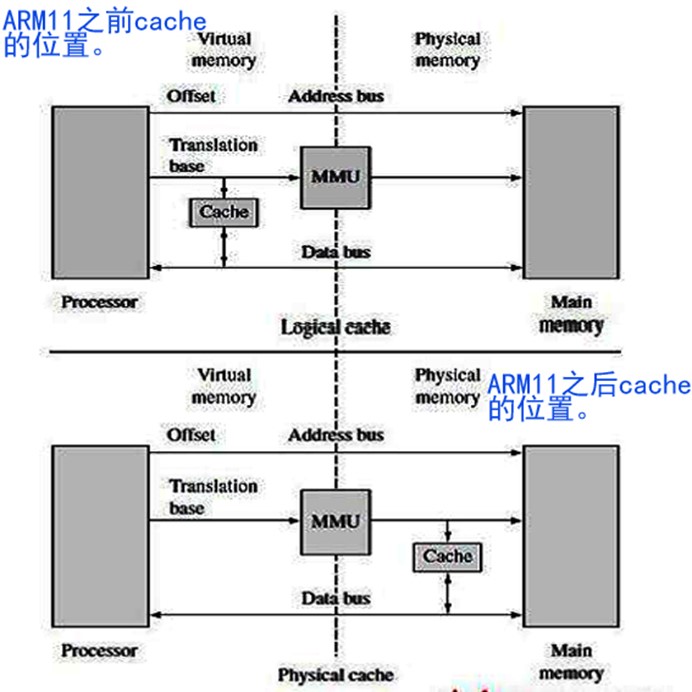

上面就是MMU的位置,完成虚拟地址到物理地址的转换。在上图结构看到cache在ARM11之前,cache是在MMU与处理器之间。ARM之后,cache是在MMU和Main memory之间。

要使用MMU和cache,这两个是必须学会使用的,这里把它关掉是我现在不用到MMU和cache,因为他们两的使用如果没有经过正确的配置,会出现一些意想不到的错误。所以这里先把他们关掉,免得出现影响裸机的学习。

2440的I、Dcache无效的设置:

首先进入ARM920t核手册ARM920T_TRM1_S.pdf,搜索CP15:

定位到2.3 CP15 register map summary

咋CP15里有一个control寄存器:

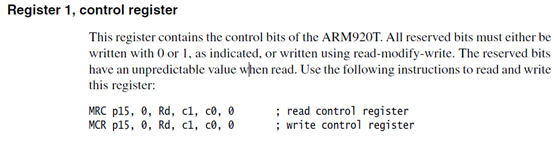

定位到该寄存器,可以看到它的访问方法read和write:

MRC p15, 0, Rd, c1, c0, 0 ; read control register

MCR p15, 0, Rd, c1, c0, 0 ; write control register

在这个寄存器中,怎么设置关闭I、Dcache和MMU,看下面control寄存器的参数:

从上图可以看到,控制I cache的是[12]位,该位设置为0就是disable I cache,1为使能。控制D cache的是[2]位,该位设置为0就是关闭D cache。第[0]位是控制MMU,设置为0是关闭,设置为1是使能。所以关闭I/D cache的工作就是设置上面三个位为0即可。

但是,在起初时,I/Dcache里面已经有了数据了的。所以我们还需要对它进行数据无效操作:

命令:

MCR p15,0,Rd,c7,c7,0

由上面的信息知道,关闭I/D cache和MMU的操作是:

-

使I/D cache和MMU无效:MCR p15,0,Rd,c7,c7,0

-

接着关闭I/D cache和MMU。

首先是使I/D cache和MMU无效,这里的通用寄存器选r2:

MCR p15,0,r2,c7,c7,0

关闭MMU和cache:

MRC p15,0,r2,c1,c0,0 @ read control register

bic r2,r2,#0x00000805 @0b100000000101=0x805

MCR p15,0,r2,c1,c0,0 @ write control register

最后的代码:

这里是2440的设置,6410和210也是一样的操作。前面提过他们三者的CP15是一样的。

6410:

MRC p15, 0, <Rd>, c1, c0, 0

MCR p15, 0, <Rd>, c1, c0, 0

MCR CP15,0,R1,C7,C10,0

MCR CP15,0,R1,C7,C10,0

210: