前仿真

后仿真

时序(综合后)仿真

时序仿真将时延考虑进去,包括综合后产生的(与、或、非)门时延,还有布局布线产生的时延。

综合(Synthesize),就是将HDL语言设计输入翻译成由与、或、非门和RAM、触发器等逻辑单元组成的网表。综合后可生成综合后仿真模型(Generate Post-Synthesis Simulation Model)。

综合后,进行ISE的实现(Implement),包括翻译、映射、布局布线。在这三个过程中都可以生成一个仿真模型(翻译和映射不会产生延时,因此常用布局布线后产生的仿真模型进行时序仿真)

进行综合:双击 Synthesize – XST ,想生成 Post-Synthesis Simulation Model,双击Generate Post-Synthesis Simulation Model即可,会在工程文件夹下生成netgensynthesiscount4_synthesis.v等文件

进行实现:双击 Implement Design ,完成后,双击Generate Post-Place & Route Simulation Model.。生成布局布线后仿真模型。

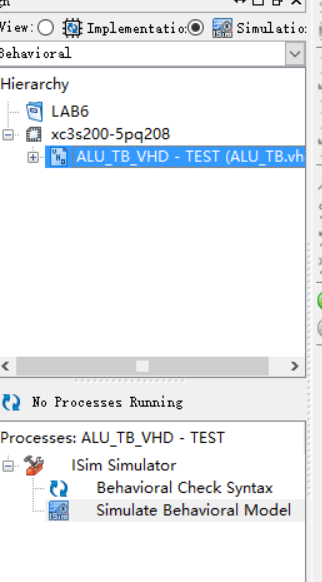

切换到 Simulation ,选中Post-route。

(4)、然后选test bench文件,双击下面的Simulate Post-Place&Route Model,启动modelsim。

在modelsim中观察仿真波形。可以看到输出有明显的延时。