计组假期预习微型指南

写在前面

首先,看到各位学弟学妹们对计组充满好奇并且想要假期预习一下计组,我本人是很高兴的,为了帮助各位学弟学妹们在预习的时候少走点弯路,我以个人名义写下这篇计组假期预习攻略。

这篇文章的本意并不是让大家一个暑假搞定全部计组内容,而是让大家对计组要做的东西有一个基本了解和心理准备。

注意:如果在阅读本文中遇到陌生名词,请务必去查一下!

什么是计组

这里我就不复制百度百科了,直接谈谈6系计组课程的一些事宜

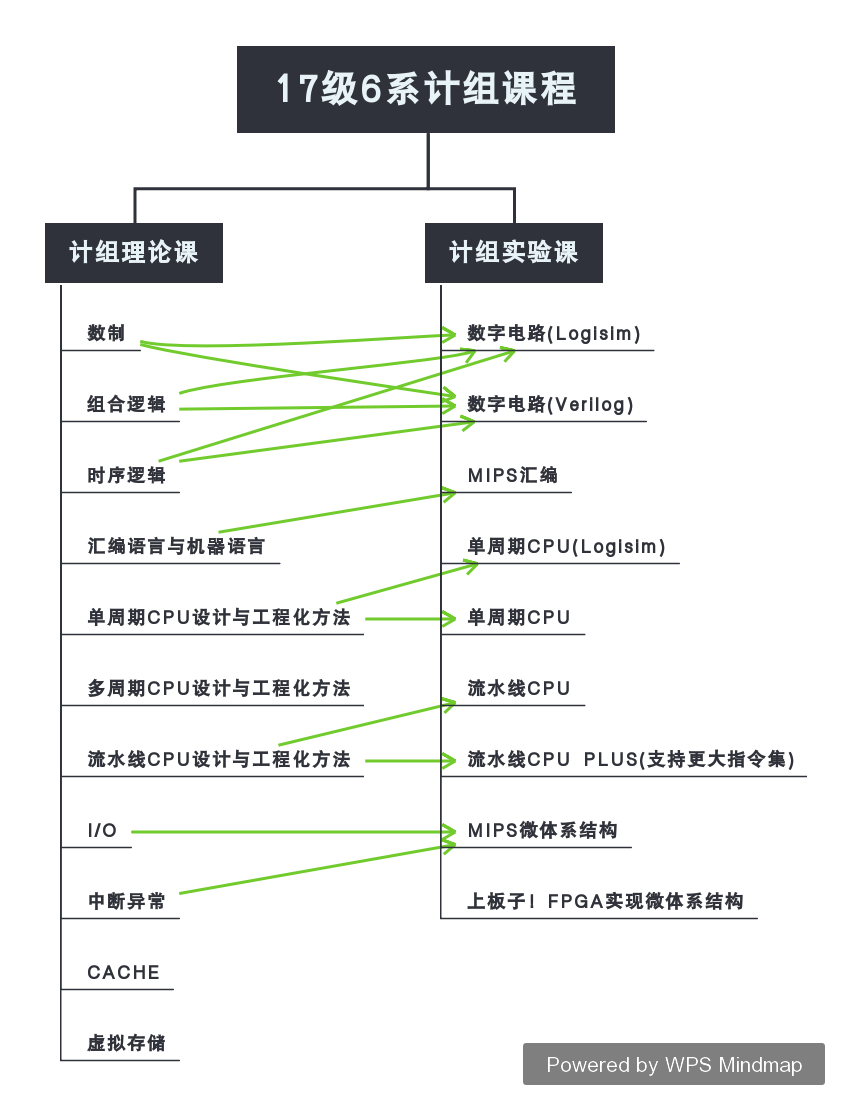

首先,计组分为两门课程。

-

计算机组成(4学分,可能变化)

这门课程主要是讲授数字电路的一些基本知识与计算机各个组成部分的理论知识。虽然,这门课程被称为计组理论课,但是,实验课要用到的方法都是在理论课上讲授,所以,万万不可掉以轻心。

这门课程的教学内容可以参考往年课件,具体方法,可以在北航课程中心搜索"计算机组成"(登陆状态可查看相应课程资源,下载课件)。 -

计算机组成课程设计(3学分,可能变化)

这就是让6系学子叫苦连天的计组大魔王了。它不仅仅需要计算机的各种原理知识与代码能力,同时是6系本科阶段第一门要求一定的工程素养的学科。对于多数人来说,这门课程会是一个前所未有的挑战。

说这门课程难,的确,多数6系本科生在此时不具备要求的工程能力,但是,就我个人看来,这门课程的难度还没到凭借努力无法克服的程度。计组课设课程内容:

大致内容是以闯关制(前一个实验如果没通过,不可以进行下一个实验)的方式来完成若干个实验。

每个实验分为课下部分与课上测试部分,计组课设的学时就是课上测试部分。课下部分虽然没有计入学时,但是占了计组课设绝大部分时间。

更多详细内容就请大家期待开学之后老师们的讲解吧,毕竟介绍课程制度不是本篇博客的目的~课程结构示意图,具体教学内容与顺序因各个老师不同而有微小差别。

计组课设涉及的工具与语言

这里将给大家简单介绍一下计组课设所涉及的工具和语言,以及一些要点。限于篇幅与本文的目的,更多的坑还需要大家自行发现。

- logisim

一款数字电路仿真软件,主要操作还是靠鼠标绘制电路连线以实现特定功能。建议诸位在预习的时候可以在熟悉这个软件的同时学习一些数字电路的基本知识。 - 汇编部分

- MIPS汇编语言

- 什么是MIPS?

MIPS是一套体系结构,可以理解为符合某一类规范的计算机的指令集架构(ISA instruction set architecture)。除此之外还有著名的x86、ARM等等。- 什么是汇编语言

大家所学习过的C语言在编译之后得到的就是汇编语言构成的代码,再经过汇编器,就可以得到直接在计算机上运行的机器语言。不同体系结构使用的是不同的汇编语言。 - 对于初学者,上面这些估计很难理解,所以建议大家先自行百度,抱着疑问去预习。

- 什么是汇编语言

- Mars

MIPS汇编语言的仿真工具。前文提到了,不同架构的计算机使用不同的汇编语言,多数同学使用的PC机也不是MIPS架构的,同时,我们希望能够清楚地观察汇编语言的执行情况,那么,我们就需要一款仿真软件,也就是本课程使用的Mars。这个软件的目的就是便于大家观察汇编语言的执行情况,并且自己动手用汇编语言编写程序。

- Verilog部分

- HDL(硬件描述语言)

用来描述数字电路构成的语言,用于构建电路模型。在大家熟悉的C程序中,代码总是一条一条地执行,即,串行。但是这在HDL中则不成立了,电路是并行的!

想要明白这一点,大家必须要明白,HDL是描述硬件的,是用代码描述一个实体,这个实体上有很多个电路,这些电路同一时刻都是在工作的。这一点必须明白,这是初学者从高级语言到HDL经常犯错的地方。 - Verilog

硬件描述语言的一种,注意,Verilog和System Verilog不是一回事。 - ISE

硬件描述语言既然被发明出来,显然不仅仅是用来光给人描述的,可以用于FPGA相关。

这里简单说说啥是FPGA,大致就是,可以烧录我们用HDL描述的电路的一块电路板。但是FPGA本身不具备将HDL转化为具体电路模型的功能。

那么,如何将HDL语言转化为具体的电路模型呢?

这就需要相应的工具了,ISE就是将Verilog转化为具体电路模型的工具。 - ISim

描述了电路模型,我们怎么在不烧录(烧录的概念您们应该在电设接触过,不过当时您们是把程序烧录到板子上,这里的烧录指的是把您们电路的设计变成一个可以使用的“板子”)到FPGA的前提下测试我们的电路是否存在BUG呢,这就需要电路仿真软件了,ISim就是ISE配套的仿真软件。

仿真软件通过模拟我们所描述的电路的运行并反馈相应现象帮助我们检查我们的电路是否能够正常运行。

- HDL(硬件描述语言)

开始计组实验预习前的准备

虽然,前文说过,计组理论课和实验课不完全重合且侧重点不一样,但是,一定的理论基础是实验课的基础,所以,请诸位开始正式的计组实验课程预习之前务必对基础的理论知识进行学习。大致可以参考以下内容。

注意!这些理论内容已经涉及了计组实验的大部分内容,没必要在预习阶段完全掌握。大家在学习理论的同时加以实践,注意同步即可

- 《数字设计和计算机体系结构》(涉及章节的章节小结,最好看看)

-

二进制基础(1.2~1.5)

-

第二章全部

-

第三章全部

-

注意!第一章至第三章可以归结为数字电路基础知识

-

第四章部分使用的不是Verilog,所以建议这一部分用后文会介绍的《Verilog数字系统设计教程》进行学习,详细内容后文介绍。

-

数字模块(5.1~5.5)

-

MIPS体系结构介绍与汇编语言学习:第六章除了x86部分都是必看!(如果存在疑惑可以阅读《MIPS体系结构透视》或查阅其他资料,此外,在这里推荐肖利民老师对应部分的教学课件)

-

CPU设计(7.1~7.7)关于CPU设计部分的学习,我觉得用这本书作为一个大致的了解即可,即,明白什么是CPU、有哪些主要模块、指令是怎么由CPU执行的、多周期CPU原理、流水线原理。真正到了CPU设计部分的话,还是建议参考高小鹏老师对应部分的课件。

-

《Verilog数字系统设计教程》(如果有觉得迷惑的地方可以自行百度)

-

基础概念与语法:第一章至第七章(第七章部分除7.7外了解即可)

-

对电路不同抽象层级的描述:第九章(9.3了解即可)

-

可综合的状态机设计:第十二章至第十三章

(注意:实际上,文中提及的有些语句写上即使了也可以综合,只是在综合的时候被忽略了,比如

initial。) -

阻塞式赋值与非阻塞式赋值的异同

理解Verilog神必的reg -

《MIPS体系结构透视》

这本书中的多数内容作为预习可能有些过火,但是这本书中有很多对于初学者起重要学习补充作用的部分,故我把这本书列入了预习范围中。- 补充内容——MIPS规范的学习:第九章和第十一章。

- 异常中断:第三章与第五章(注意!这部分内容已经是计组实验中靠后部分的内容,建议在能够实现流水线CPU之后再进行学习)

-

往届计组实验指导书

指导书中包含了本次的实验目标与一些基本的提示信息,本人提供的资料中不包含这些内容。 -

高小鹏老师的教学课件

如果您们觉得前文所提及的资料太难、太多难以直接入门的话,可以先通过高老师的教学课件入门,然后阅读资料深化认识。

上述资料大抵都能在课程中心通过搜索"计算机组成"找到,我只是一个搬运工~

附赠资料

某盘链接:

链接:https://pan.baidu.com/s/1aHy1MZfPMXRMlh3Md3tFfg

提取码:249m

切记,理论和实践并重。完完全全把理论学完了再来实践是不行的!

预习目标

前文介绍了需要的理论知识,并没有把每一部分实验需要哪些理论基础给大家做一个说明,下面就完成这件事。

这里给大家按照难度级别划分几个预习目标(难度逐级增加),大家量力而为。

-

难度一

熟悉logisim的基本使用,能够使用logisim构建具有一定功能的时序电路(可以参考高老师课件的课后作业部分也可以参考《数字设计和计算机体系结构》的部分课后习题)需要的理论基础

- 数字电路基础知识

-

难度二

熟悉Mars的基本使用能够用MIPS汇编编写具有一定功能的程序并且具备使用Mars调试汇编代码的能力。练手题目可以根据大家学习C语言时做过的题目进行练习。

需要的理论基础- 数字电路基本知识

- MIPS汇编基础

- MIPS软件标准 《MIPS体系结构透视》(进阶内容)

-

难度三

注意!本部分建议与Verilog的学习同步进行成功安装ISE(不要安装Win10版!),熟悉ISE的使用,尤其要懂得综合(synthesize)功能的使用。学会使用ISIM进行电路仿真与调试。

练手题目可以参考 难度一 部分的题目,不过这回是要用Verilog实现,建议尝试 门电路级别描述 与 行为级别描述 两种方式。

警告:这个部分看起来难点在于Verilog的学习,

实际上ISE与ISIM的使用是一个不亚于Verilog的难点。ISE与ISIM的使用对计组学习影响重大,请大家一定要好好熟悉这个工具需要的理论基础

- 数字电路基本知识

- Verilog语法知识

-

下面就是CPU设计部分的内容了,大家可以参考高老师的课件进行学习

-

难度四

这个任务主要是让大家直观地感受什么是CPU,所以,在预习阶段,没必要在这个任务上苛求完美使用logisim实现单周期CPU,指令集可以参考《数字设计和计算机体系结构》对应部分内容,自行用Mars编写汇编代码并导出机器码,将机器码导入logisim中CPU的模块中进行测试

-

难度五

把 难度四 中的CPU通过Verilog实现

其中,测试程序的导入可以通过Verilog的$readmemh实现,如果不仅仅希望通过仿真波形进行观察,还可以加入$display进行调试。 -

难度六

实现一个多周期CPU,指令集参考《数字设计和计算机体系结构》对应内容。为什么不让您们实现流水线呢?因为一个暑假预习到能够实现流水线的程度不太现实。

有关软件的一些教程

Logisim

Mars

这个软件教程不多(实际上,功能也不复杂,大家摸索下基本上都能玩明白)

多用HELP功能是好习惯。

ISE

ISE安装教程(笔者当时预习的时候是按照这个教程来的,如果不能用的话大家就再四处找找,配环境是挺麻烦的的步骤)

ISE基本使用教程(看到波形仿真即可,后面的板级综合暂时用不到)

ISIM使用指南(这个教程当年救了笔者的狗命)

如果这些教程还不够的话,大家自己再找找鸭~ 自主寻找资料迟早都要经历的鸭~

结语

笔者所列举的预习内容确实有些多了,并且在学习顺序上也可能存在着不完善的地方,希望大家在学习过程中根据自身情况进行取舍。

最后,再次重申和提醒,这篇文章并没有也做不到把计组全部的坑给列出来,仅仅是给各位希望预习计组的同学指一条不那么弯的路,具体的学习还望大家发挥主观能动性。