本文转自:自己的微信公众号《集成电路设计及EDA教程》

以后打算交替着推送多种EDA工具的教程而不只是单纯针对某个工具,依次来满足不同粉丝的需求。

这里分享一篇多年之前写的推文,虽然时间比较久了,但是非常实用,非常受欢迎。

《ICC中对Skew进行Debug的好工具--Interactive CTS Window》

CTS无疑是数字后端中一个除了Floorplan之外最复杂的一个步骤,因为这一步可能会需要很多人为的分析以及操作。

用一个例子(该例子有一个主时钟、一个它的分频时钟,此外还做了DFT,插入了scan chain、boundary scan)来讲解如果CTS之后发现自己是设计的Skew很大该如何去Debug。后边会用一个长文来讲解做时钟树过程中遇到的问题以及尝试解决该问题的步骤,其中Debug主要用的就是这个工具。

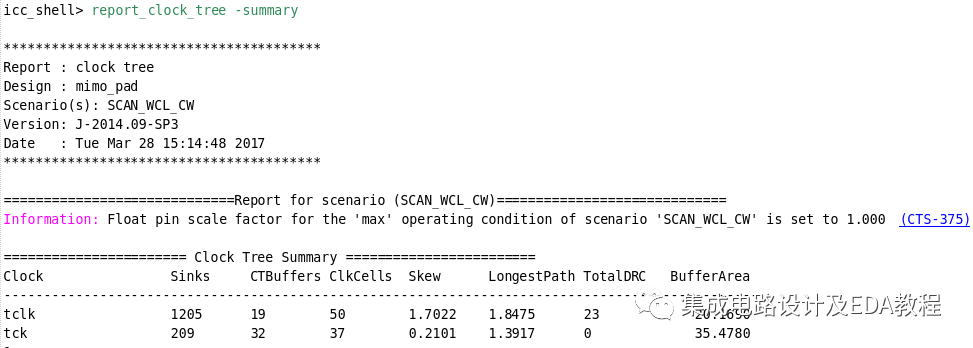

>report_clock_tree -summary (报告的是Global Skew)

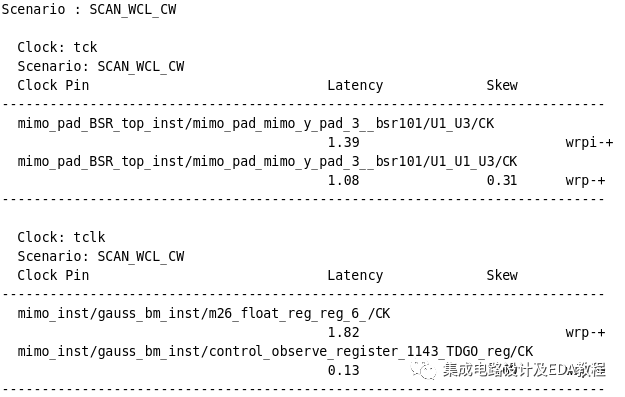

>report_clock_timing -type skew (报告的是Local Skew)

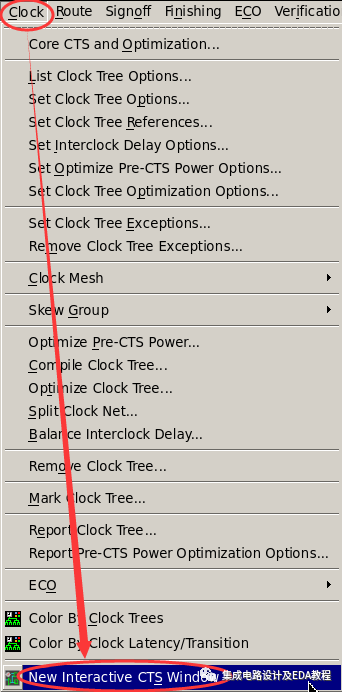

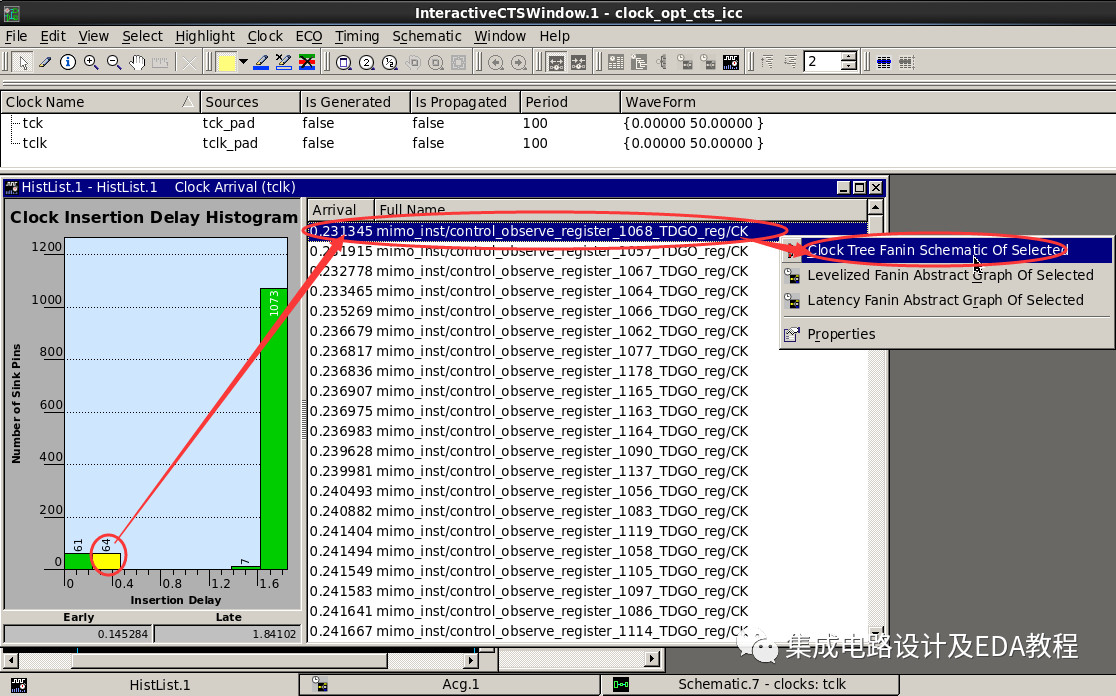

从上图发现,Skew很大,那么该如何进行Debug呢?可以使用菜单栏中的Clock> New Interactive CTS Window。

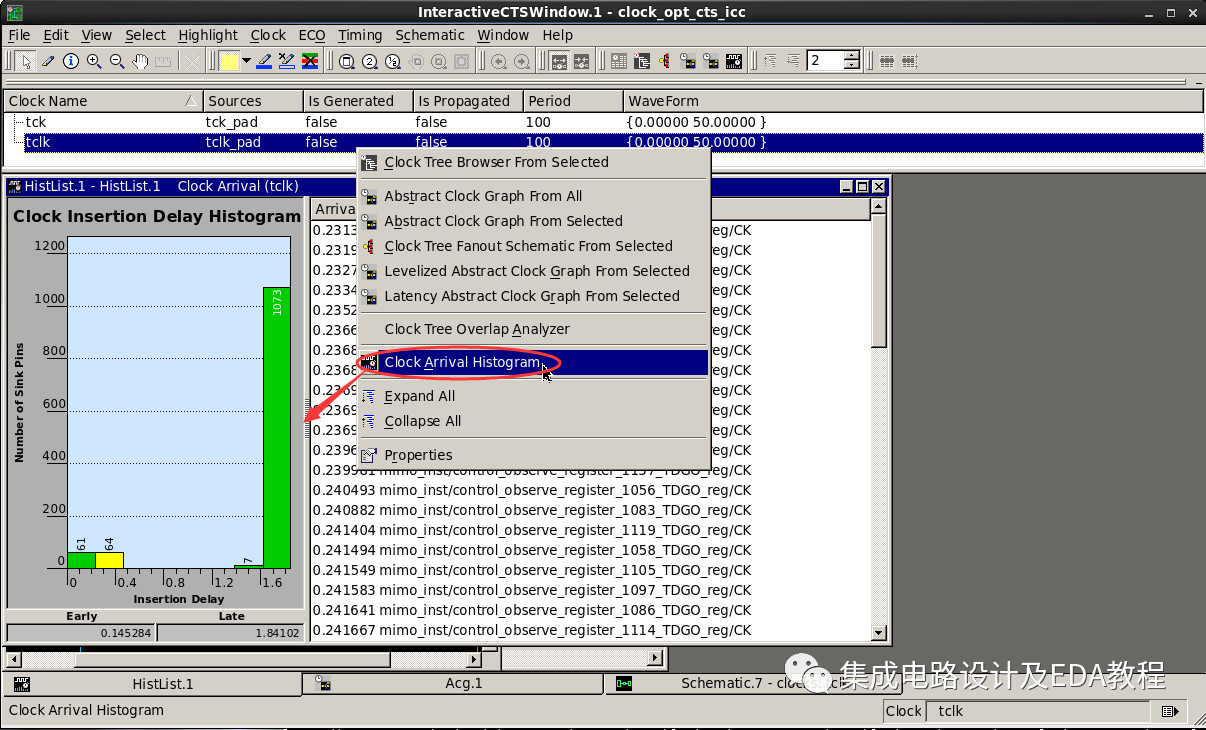

ICC会显示出设计中的时钟树名称,可以右键点击任意一个时钟树,选择Clock Arrival Histogram来生成时钟树信息柱状图。

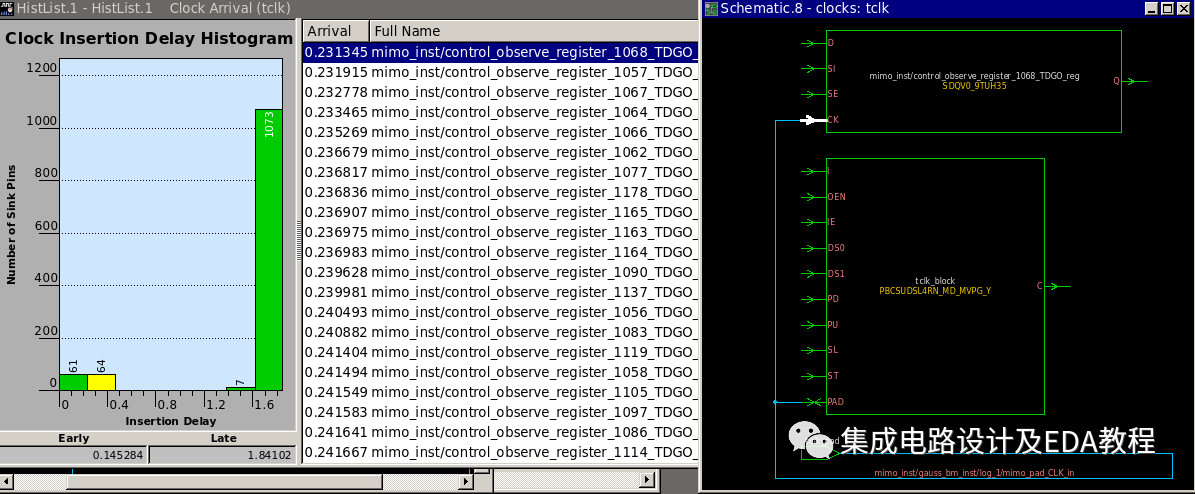

根据该图能非常方便的查找Skew很大的原因。如果在时钟树中没有找到时钟树,可能改时钟树并未出现在当前的scenario里面,可以用current_scenario来切换当前scenario,并用report_clock_tree -clock_trees“clock_name”来报告相关时钟信息,然后就可以在New Interactive CTSWindow窗口中看到了。如果不执行report_clock_tree -clock_trees “clock_name”命令,还是无法看到的。

可以非常明显的发现,所有CTS存在问题的地方都是发生在control_observer_register(DFT插入的test point用于提高故障覆盖率)的CK端上,且他们还都是直接接到tclk_pad上了,没有经过IO tclk_block。说明在DC综合的时候control_observer_register的CK端没有hookup到正确的tclk_block/C上面。

修改之后上面的问题就不存在了。

更多资料欢迎移步微信公众号《数字集成电路设计及EDA教程》

网易云课堂视频课程

链接:https://study.163.com/course/introduction/1005909004.htm

Calibredrv教程-提高流程自动化

## 为了方便大家交流讨论 ##

## 建了一个QQ群 ##

## 集成电路设计及EDA教程 ##

## 加群请备注:EDA ##

## 群二维码如下 ##

# 本公众号有个红包和资料福利微信群 #

# 集成电路设计及EDA教程福利群 #

# 为了避免乱七八糟的人加进来 #

# 可以先加我微信,我拉你进群 #

# 加我微信 请备注下面问题的答案 #

# ASIC的全称 #