本文转自:自己的微信公众号《集成电路设计及EDA教程》

《ICC教程 - Flow系列 - 概念系列 - ECO (理论+实践+脚本分享)》

这篇推文讲一下数字IC设计中的post mask ECO和premask ECO,并讲解一下在ICC中Apply ECO的流程。

理论:

ECO分为post mask ECO和premask ECO,也就是只修改metal layer的ECO和任何layer都可以动到的ECO。

Post mask ECO:

Post mask ECO是利用预先留好的备用单元(Spare Cell),做的逻辑修改。如果后期发现Timing存在问题(或者想小动Function),可以利用附近的Spare Cell搭配上层金属连线来修改电路结构。这种ECO受限于Spare Cell的位置,如果附近找不到的话,就比较麻烦了,所以它的修改规模十分有限。

Spare cell:

Foundry提供一种服务,允许客户在wafer加工到poly以及M1层的时候,让大部分wafer暂时停止加工,而少量wafer继续加工直至完成。之后可以对这些完成了的wafer上的die进行测试,如果发现存在功能或者时序上的问题,那么可以通过利用那些预布在die上的spare cell来解决。由于绝大部分的金属层都没有加工,因此在不修改标准单元布局的情况下(也就是不用改动M1以及poly、NW、SP、SN等这些base层的mask,在流片过程中这些层的光刻也是最贵的),只用改动几层金属的mask并利用spare cell去修复这些问题。如此一来,也大大降低了流片的风险,试想,如果直接让所有的wafer都加工完成,测试后发现存在bug,那么几百万刀的流片费用变付之东流,这个还不是最重要的,最重要的是产品上市时间delay了。而Post mask ECO则提供了一种根据silicon测试结果进行Debug的方法。

Premask ECO:

Premask ECO比post mask的要灵活得多。在tapeout之前,如果发现有任何需要修改的地方,都可以用这种方法。它可以改几百个,甚至上千个单元。该操作主要是针对静态时序分析和后仿真中出现的问题,对电路的网表直接进行修改,待网表修改完毕之后反馈到PR工具中对标准单元的布局和连线进行小范围的改动。当然,直接对网表进行修改是存在风险的,所以之后一定要进行形式验证(formal verification)。

ECO修改组合逻辑比较容易,如果动到FF的话,要格外小心,因为它有可能影响clock tree,进而造成大量的时序违反。

流程、实践与脚本分享:

下面以ICC中用ECO的方法修hold违反为例简单讲解ICC中进行premask的ECO方法。

首先在PT中用以下命令修hold:

>fix_eco_timing -hold

之后通过下面的命令来导出PT对网表做出的改动,格式为ICC的tcl脚本格式。

>write_changes -format icctcl -output eco_fix_hold.tcl

接着便可以开始ICC中的ECO流程了,先在ICC中加载PT导出的tcl文件来更改ICC中的网表。

>eco_netlist -by_tcl_file eco_fix_hold.tcl

接着便是在版图中放置那些网表中新加入的Cell,如果设计中之前已经加过Core Filler了,需要执行下面的命令:

>place_eco_cells -eco_changed_cells

-legalize_only

-remove_filler_references "$FILLER_CELL_METAL $FILLER_CELL"

如果之前还没有加入Core Filler,那么只需要执行下面的命令即可:

>place_eco_cells -eco_changed_cells -legalize_only

放置完新加入的Cell之后还需要对设计重新插入Core Filler,即先插入带金属的Filler,再插入那些不带金属的Filler。

之后进行电源地的逻辑连接,

# Connect PG nets

> derive_pg_connection

-power_net {VDD} -power_pin {VDD}

-ground_net {VSS} -ground_pin {VSS}

> derive_pg_connection -power_net {VDD}

-ground_net {VSS} -tie

其中,legalize_placement可以使用check_legality -verbose查看是否有不合法的标准单元布局。由于此时的布线只是少量改动,因此完全可以禁用时序驱动以减少运行时间。

## 然后进行ECO route

>set_route_zrt_global_options -crosstalk_driven false

-timing_driven false

>set_route_zrt_track_options-crosstalk_driven false

-timing_driven false

>set_route_zrt -detail_options -timing_driven false

>route_zrt_eco -reroute modified_nets_first_then_others

执行ECO后如果有DRC问题,可以紧接着执行route_zrt_detail,这可以修复绝大部分DRC。

>route_zrt_detail -incremental true

-max number iterations 20

如果ECO改动比较小,可以用一个包含网表编辑命令组成的Tcl文件以及eco_netlist -by_tcl_file命令来更新整个设计。如果使用的是freeze silicon的ECO flow,则必须在该命令后边加上-freeze_silicon选项。当然也可以直接在命令行中输入这些网表编辑命令,或者直接source该Tcl文件。

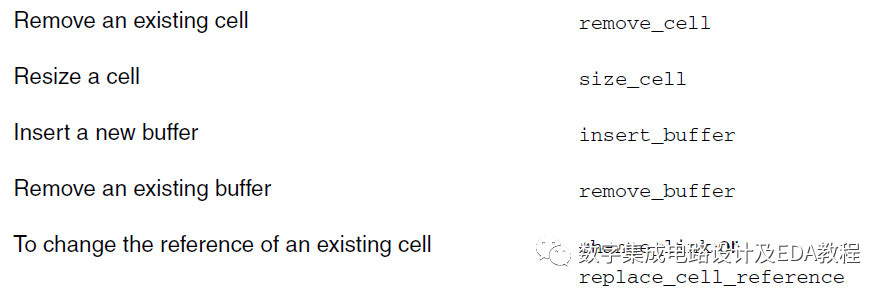

无约束ECO flow中的网表编辑命令有:

下篇推文讲解一下在PT中进行ECO的方法并分享一下脚本。

更多资料欢迎移步微信公众号《数字集成电路设计及EDA教程》

网易云课堂视频课程

链接:https://study.163.com/course/introduction/1005909004.htm

Calibredrv教程-提高流程自动化

## 为了方便大家交流讨论 ##

## 建了一个QQ群 ##

## 集成电路设计及EDA教程 ##

## 加群请备注:EDA ##

## 群二维码如下 ##

# 本公众号有个红包和资料福利微信群 #

# 集成电路设计及EDA教程福利群 #

# 为了避免乱七八糟的人加进来 #

# 可以先加我微信,我拉你进群 #

# 加我微信 请备注下面问题的答案 #

# ASIC的全称 #