1. 有这个板子使用的是Artix-7系列的XC7A100T-1CSG324C芯片。作为7系列中的一款FPGA,这个芯片的结构与Kintex-7和Virtex-7几乎一样。也配备了XADC。在Artix-7系列中,100T和200T与其它芯片不同,这两款是ISE与Vivado同时支持的芯片,而更小的35T,50T和75T,ISE的支持会相对差一些。从这个角度说,100T的可玩性比较大。这也是Nexys-4比Avnet Artix-5 50T板子要好一些的地方。

2. 打算用数码管驱动测试一下。打开vivado2014.2软件,创建工程

3. 增加文件,shumaguan.v,代码比较简单。

1 `timescale 1ns / 1ps 2 module shumaguan(seg,dig,clock,); 3 input clock; 4 output [7:0] seg; //数码管段码输出 5 output [3:0] dig; //数码管位码输出 6 reg [7:0] seg; //数码管段码输出寄存器 7 reg [3:0] dig; //数码管位码输出寄存器 8 reg [3:0] disp_dat; //显示数据寄存器 9 reg [36:0] count; //定义计数寄存器 10 always @ (posedge clock ) 11 begin 12 count = count + 1'b1; 13 dig= 8'b1110;// 14 end 15 always @ (count[24]) 16 begin 17 disp_dat = {count[28:25]}; 18 end 19 always @ (disp_dat) 20 begin case (disp_dat) 21 4'h0 : seg = 8'hc0; //显示"0" 22 4'h1 : seg = 8'hf9; //显示"1" 23 4'h2 : seg = 8'ha4; //显示"2" 24 4'h3 : seg = 8'hb0; //显示"3" 25 4'h4 : seg = 8'h99; //显示"4" 26 4'h5 : seg = 8'h92; //显示"5" 27 4'h6 : seg = 8'h82; //显示"6" 28 4'h7 : seg = 8'hf8; //显示"7" 29 4'h8 : seg = 8'h80; //显示"8" 30 4'h9 : seg = 8'h90; //显示"9" 31 4'ha : seg = 8'h88; //显示"a" 32 4'hb : seg = 8'h83; //显示"b" 33 4'hc : seg = 8'hc6; //显示"c" 34 4'hd : seg = 8'ha1; //显示"d" 35 4'he : seg = 8'h86; //显示"e" 36 4'hf : seg = 8'h8e; //显示"f" 37 endcase 38 end 39 endmodule

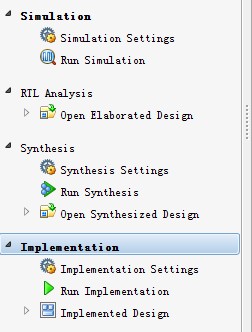

4. 先点击Simulation功能仿真,然后Synthesis综合,综合完之后,在Implementation下面Implemented Design会从灰色切换到可点击状态。

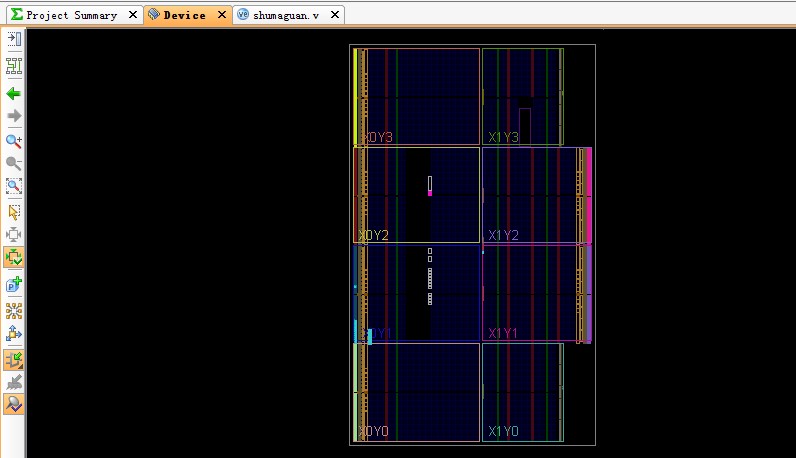

5. 看下器件的内部结构图,大致分为8个区域

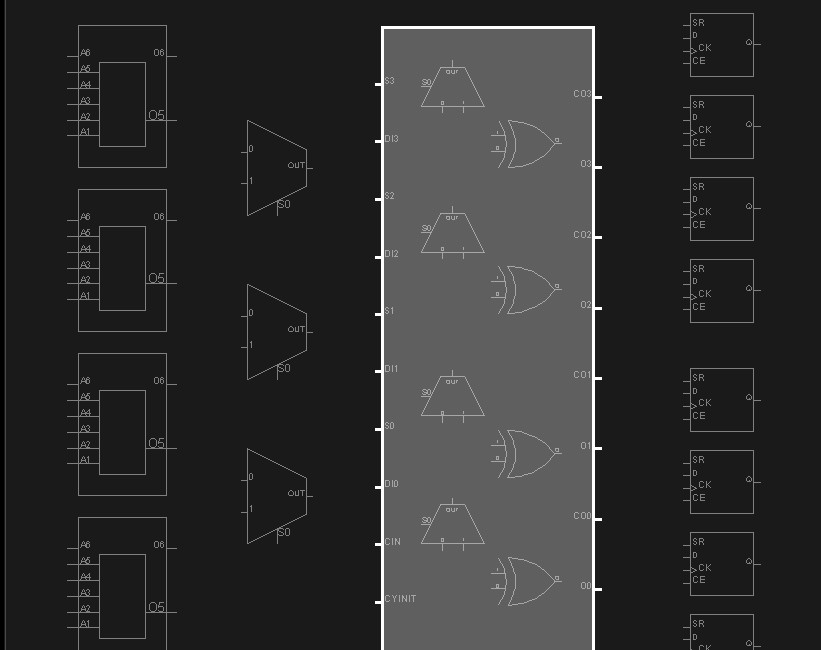

6. 放大看下内的结构,这个有时间要研究下了。感觉是技术核心。

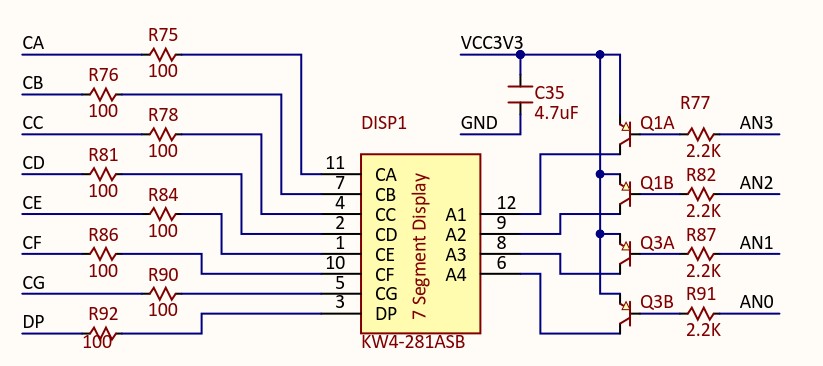

7. 配置引脚,打开I/O Ports这个界面,在site栏选择需要的引脚,电平选择LVCOMS33,看下原理图

8. 看下引脚对应的

1 ## 7 segment display 2 #NET "ca" LOC=T10 | IOSTANDARD=LVCMOS33; #IO_L24N_T3_A00_D16_14 3 #NET "cb" LOC=R10 | IOSTANDARD=LVCMOS33; #IO_25_14 4 #NET "cc" LOC=K16 | IOSTANDARD=LVCMOS33; #IO_25_15 5 #NET "cd" LOC=K13 | IOSTANDARD=LVCMOS33; #IO_L17P_T2_A26_15 6 #NET "ce" LOC=P15 | IOSTANDARD=LVCMOS33; #IO_L13P_T2_MRCC_14 7 #NET "cf" LOC=T11 | IOSTANDARD=LVCMOS33; #IO_L19P_T3_A10_D26_14 8 #NET "cg" LOC=L18 | IOSTANDARD=LVCMOS33; #IO_L4P_T0_D04_14 9 #NET "dp" LOC=H15 | IOSTANDARD=LVCMOS33; #IO_L19N_T3_A21_VREF_15 10 11 #NET "an<0>" LOC=J17 | IOSTANDARD=LVCMOS33; #IO_L23P_T3_FOE_B_15 12 #NET "an<1>" LOC=J18 | IOSTANDARD=LVCMOS33; #IO_L23N_T3_FWE_B_15 13 #NET "an<2>" LOC=T9 | IOSTANDARD=LVCMOS33; #IO_L24P_T3_A01_D17_14 14 #NET "an<3>" LOC=J14 | IOSTANDARD=LVCMOS33; #IO_L19P_T3_A22_15 15 #NET "an<4>" LOC=P14 | IOSTANDARD=LVCMOS33; #IO_L8N_T1_D12_14 16 #NET "an<5>" LOC=T14 | IOSTANDARD=LVCMOS33; #IO_L14P_T2_SRCC_14 17 #NET "an<6>" LOC=K2 | IOSTANDARD=LVCMOS33; #IO_L23P_T3_35 18 #NET "an<7>" LOC=U13 | IOSTANDARD=LVCMOS33; #IO_L23N_T3_A02_D18_14

9. 修改I/O Ports,修改完之后,Ctrl+S保存一下,会让保存一个文件,XDC格式的。

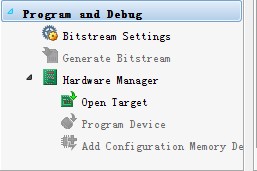

10. 插上板子USB接口J6,等待驱动识别,点击生成二级制文件Generate Bitstream。需要的时间比较久,耐心等待

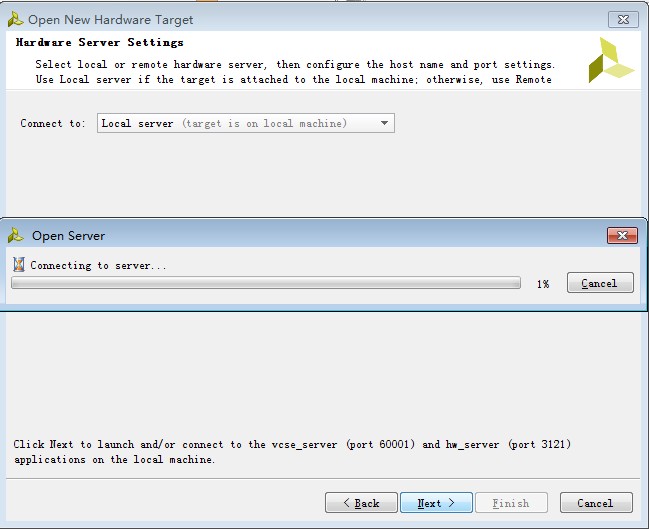

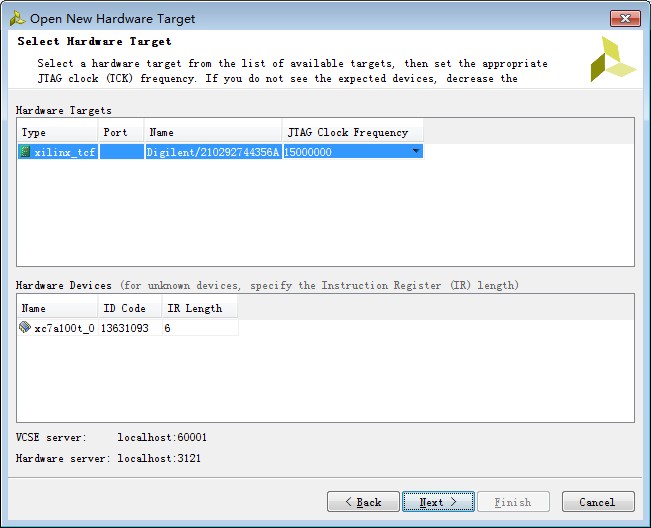

点击Open Target

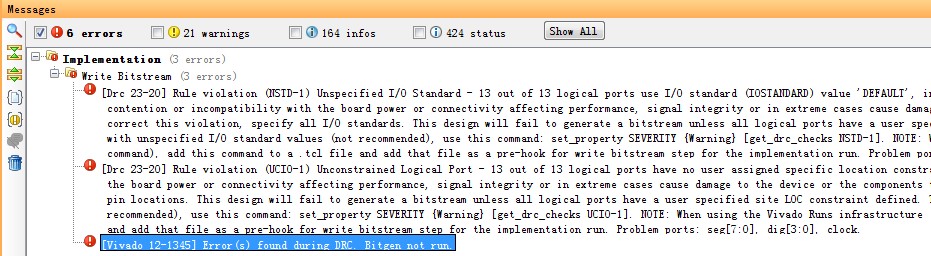

11. 看到到的XADC,是内部的ADC吗?生成2进制文件的时候,遇到一个错误

12. 网上说法是将下面保存成.tcl文件

1 set_property SEVERITY {Warning} [get_drc_checks NSTD-1] 2 set_property SEVERITY {Warning} [get_drc_checks RTSTAT-1] 3 set_property SEVERITY {Warning} [get_drc_checks UCIO-1]

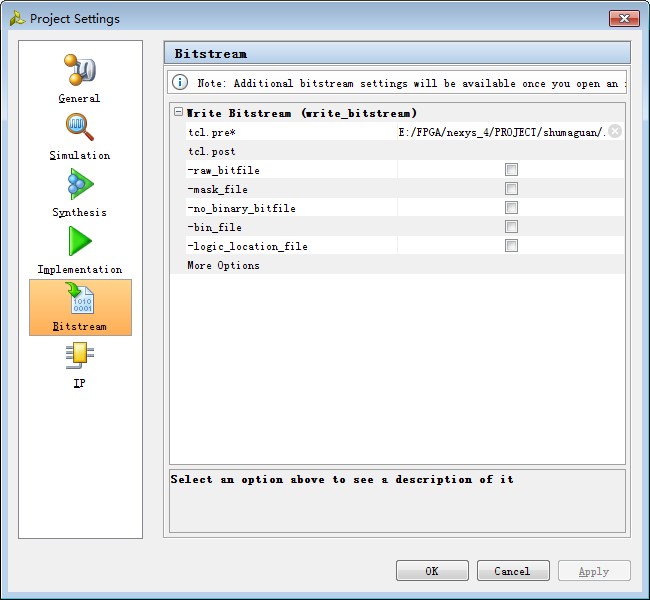

再到bitstream settings做如下设置即可:

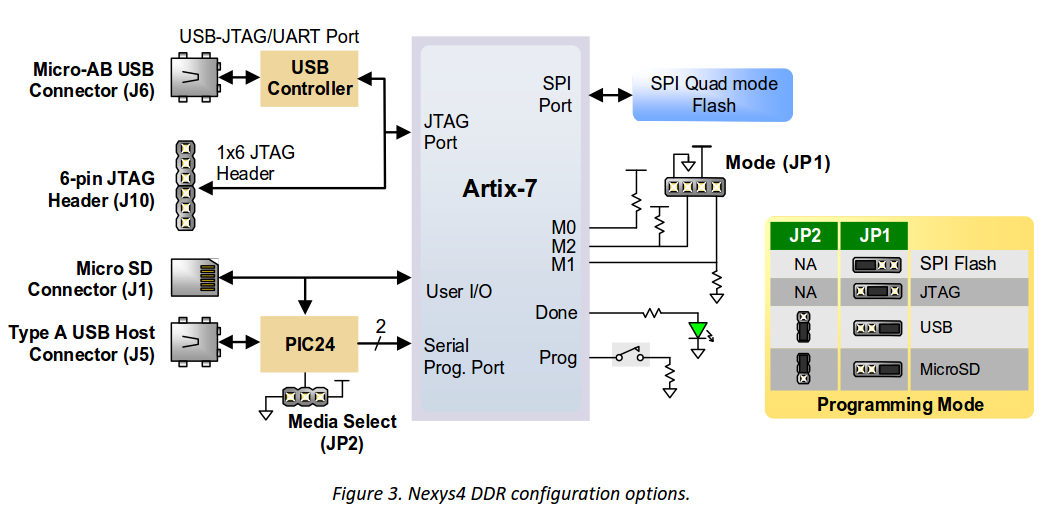

13. 最后Program Devices。不过烧写之后,程序并没有运行,所以我检查了一下,跳线帽,主要是JP1和JP2的选择,本次是用JTAG烧写的,编程烧写成功之后,Done灯会亮,但是不知道亮多久。Prog按键是按下会复位FPGA内部的配置内存,并且按照下图的编程,重新从外置器件读取配置信息到FPGA内部的配置内存。

14. 最后数码管正常运行。