在scan stitch之后,scan synthesis就已经完成,

Scan extraction主要用来从scan design中extracing所有的instance,来保证scan chain的完整性。

并保证所有的design change都整合到scan design。

Scan Verificaiton

1)在shift operate中的hold time violation,如果两个scan cell是同时钟,需要由CTS来保证clock skew有一个

minimum的值。如果clock属于异步clock,需要插入lock_up latch。

2)错误的scan initialization sequence,不能进入test mode。

3)不完整的scan design rule的check和repair,reg的set/reset以及clock的enable/gate等。

4)scan synthesis的错误,将positive放在negative之前等。

scan capture操作可能会在zero_delay和full_timing之间有mismatch。

Verifying the scan shift operate:

使用一种flush test的测试用例,用full_timing的simulator,来保证数据从scan input到scan output的时钟数相同。

为了保证clock skew也满足要求,用例使用"01100"这样的数值,包含0-0,0-1,1-0,1-1所有的场景。

为了快速定位错误的scan cell的位置,flush testbench需要有可以observe到内部scan cell的处理。

1)scan hold time violation in different clock,Lock-up latch插入。

如果一条scan chain中有多个clock,每个clock之间的latency不同,design要求,保持在半个cycle之内,

所以加入一个negative的latch可以解决这个问题。

2)scan hold time和setup time in same clock,CTS redone或者插入buffer。

3)保证所有的negative-edge都在positive-edge前边,或者加入lock-up FF。

Verify the scan Capture operate:

1)通常应用一个broadside-load的testbench,直接将整个test pattern移动到scan cell中,只包含一个clock的

shift cycle和一个clock的capture cycle。

目前也都可以通过STA的方式来进行scan shift和scan capture的verify。

Scan Design Costs:

1)area overhead cost,包括两部分,scan cell与FF的替换,以及scan routing的部分。

2)I/O pin cost,包括一个dedicate test mode pin(可以通过一个initial sequence来避免)

以及I/O的shared with function。

3)performance degradation cost,增加了functional path的delay。

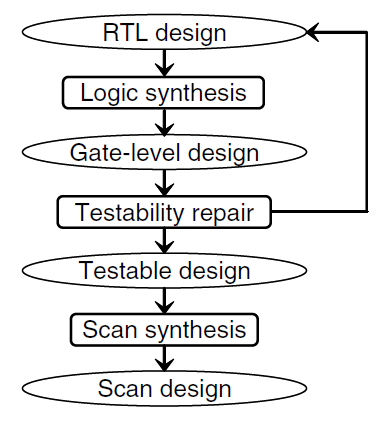

4)Design effort cost,在正常flow之外还需要进行design rule checking and repair,scan synthesis,

scan extraction,scan verification。

scan design的其他purpose:

总结来看,有enhanced scan,snapshot scan,error_resilient scan,system debug,soft error protection。

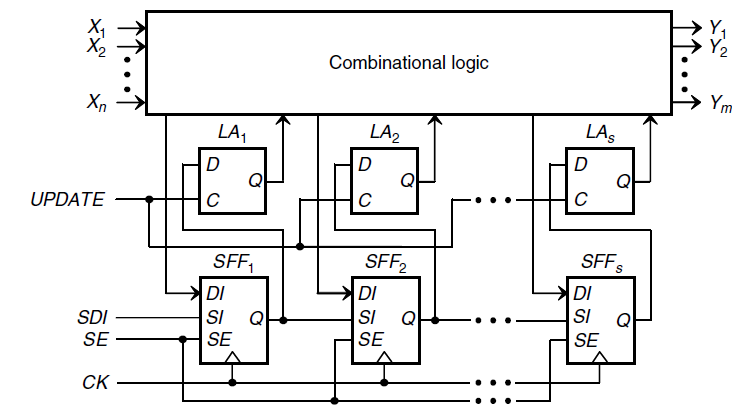

1)enhanced design,增加的delay fault detection。其中一种结构中增加一个Latch,每次锁存两bit的数据。

同时做STA时,也会增加很多false path。

2)Snapshot Scan,可以在不打断logic的functional operation的同时,capture到internal states of element。

设计通过在需要的storage element上增加scan cell来实现(不是替换),这样的设计叫做,scan set。

RTL DESIGN FOR TESTABILITY:

由于time-to-market的关系,越来越多的testability issues希望在RTL阶段得到fixed。

通过在netlist进行testability repair来,形成一个环路,每做一次testability repair需要进行重新DC。