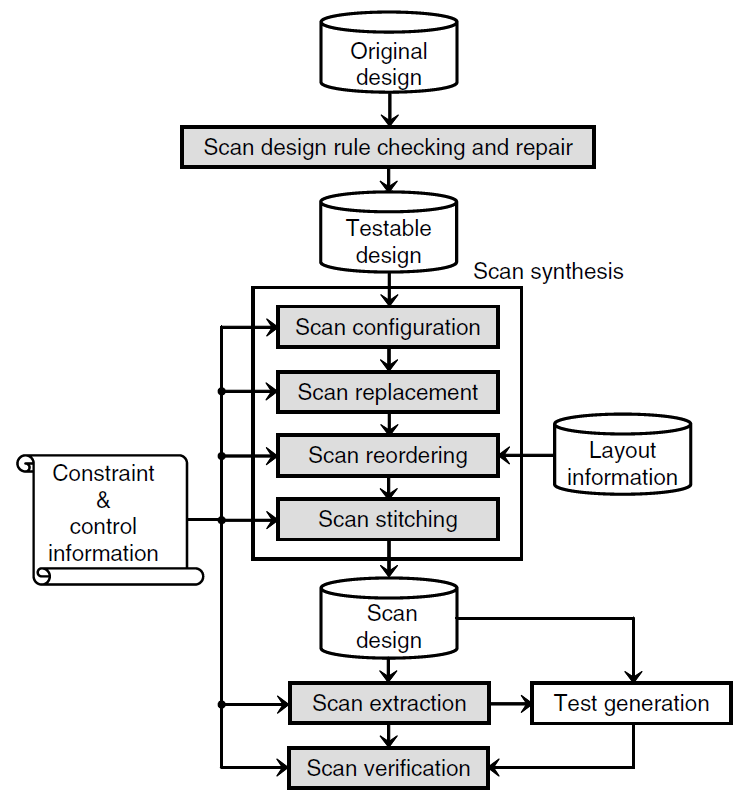

一个典型的scan实现的flow:

clock mux和一些rst,在Scan中都被bypass掉,是不能测到的。所以DFT的test coverage一般就在97%或98%。

scan design rule checking and repair:

可以在presynthesis RTL design或者postsynthesis gate-level design上进行,

经过scan repair之后的design,称为testable design。

scan synthsis是将一个testable design转换为一个scan design,目前design中会包含好几条scan chain。

scan extraction是将最终scan chain的结构提取出来,供ATPG使用。

scan verification针对shift,capture操作,进行response的验证。

Scan Design Rule Checking and Repair

进行scan design rule的check,某些clock control structure需要修改来增加at-speed test。

scan design rule的check也可以在scan synthesis之后,来保证没有新的violation出现。

在shift操作中,所有的clock都可以通过external pin来控制,在相邻的两个scan cell之间的

clock skew必须保证不会引起shift failure。

在capture操作中,data path的originate/terminate的clock可能是不一样的,这时需要考虑

timing来保证capture操作的正确。

Scan Synthesis

scan synthesis将一个testable design转变为一个scan design。

在1990年,scan synthesis的操作是一些分散的tools,将logic synthesis后的gate_level

netlist进行处理。

最近,scan synthesis的操作已经集成在了logic synthesis中,这样的处理,称为one-pass

synthesis或者single-pass synthesis。

主要包括四个部分:1)scan configuration; 2)scan replacement; 3)scan reordering;

4)scan stitching;

scan chain主要包括:

1)the number of scan chain;

2)the type of scan cells to implement these scan chain;

3)storage element to be excluded from scan synthesis;

4)the way of scan cell arranged in scan chain;

scan chain number主要由电路的input和output的个数来决定,high-speed的IO pad是不能

被用来做scan IO复用的。

scan cell的type,主要由lib来决定,一般每一种使用的storage element都会有相应的scan cell type,

来保证functionality和timing在正常操作下,被影响的最小。

exclude的storage element主要因为critical path或者security reason等。

storage element的arrange,主要由这些scan chain上的clock domain的多少来决定。

一般情况下,一个scan chain由属于同一个clock domain的scan cell组成,(因为在DC过程中,整个scan chain是一条data path

此时的异步逻辑在DFT中也会是同步的处理。)

当一个clock domain包含很多的scan cells时,一些scan chain会被结构化的实现,scan-chain operation被用来减小scan-chain的长度。

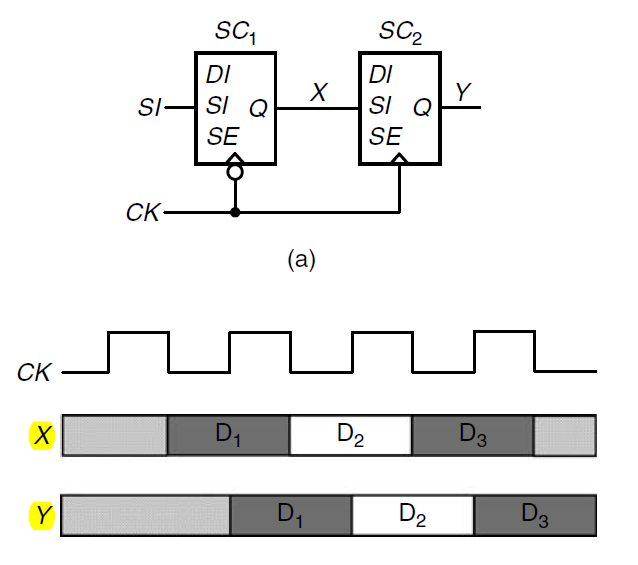

当一个scan-chain中既包含negative-edge scan cell又包括positive-edge scan cell时,negative的scan cell

应该放在positive scan-cell的前边。(为了clock一个周期只移动一位)

scan-chain的长度尽量平衡,方便并行化。

如果positive scan-cell放在前边,那么这两个cell在一个clock周期内,都会shift data。

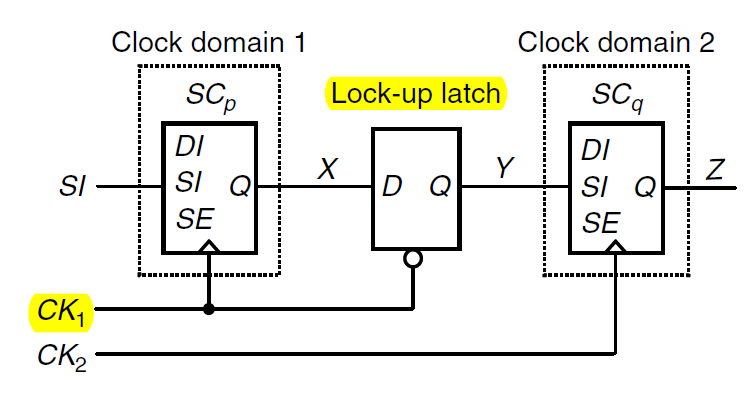

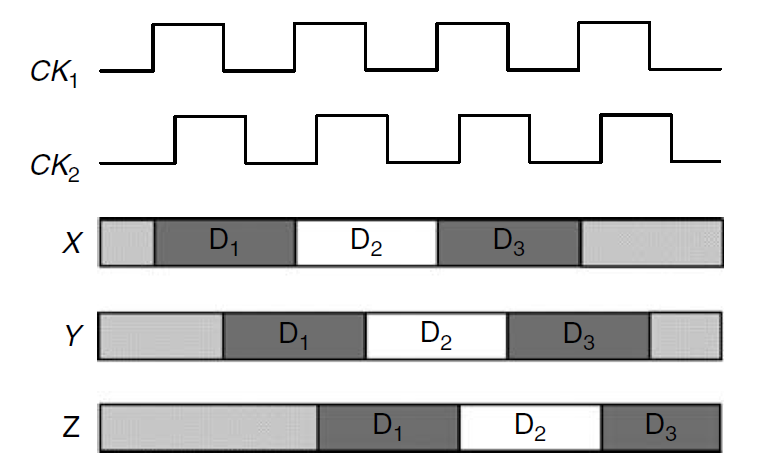

当一个scan-chain的scan cell来自不同的clock domain时,一个lock-up latch需要插入。

这样可以保证,不论CK2优先CK1还是CK1优先CK2,shift的操作都是正确的。

但是必须保证CK1和CK2之间的skew少于一个duty cycle。

当scan chain的clock结构定下来以后,进行scan cell的stitch到scan chain以及这些scan cell的

place,stitch以最小化scan routing为目标。

Scan Replacement:

经过scan configuration,scan replacement将storage element替换为functionally equivalent scan cell

这时的design叫做,scan-ready design。

这些scan cell的input通常连接到同一个scan cell的output来避免floating。这些连接在stitch阶段去除。

目前,在RTL阶段也可以实现部分的scan replacement。

Scan Reordering

反应scan chain中scan cell的reorder。在物理实现之前,一个random的scan order被design使用。

在进行physical implementation时,scan order可以使用intra_scan_chain reordering(scan cell只在该scan

chain内进行reorder)和inter_scan_chain reordering(scan cell在不同的scan chain之间reorder)

scan stitching

将所有的scan cell stitch到一起,组成scan chain。将每一个scan cell的output连接到下一级的input。

将第一个scan cell的input连接到primary input,最后一个scan cell的output连接到primary output。

在stitch的过程中,需要插入一些lock_up的latch和lock_up的FF来保证shift操作正确。