在一个cell library中,比较重要的是cell height,cell height由tracks来决定,track表示一个metal线的pitch。

一个cell通常被做成一定数量的tracks,主要由timing和routing来进行优化。

1)Tall track height library可以支持复杂的routing,更大的drive strength,但是leakage和area较大。

适用于perormance要求比较大的地方。一般会有11-12track。

2)low-track height library,适用于area efficiency的区域,相应的drive strength较小。一般有7-8track。

3)standard track height library,drive strength与area之间的trade-off。

根据不同的threshold voltage来进行分类:

1)high-Vt library,适用于non-timing-critical design,leakage较小,timing较差。

2)low-Vt library,适用于speed logic。leakage较大。

3)Regular/Standard library,leakage和speed之间的trade-off。

长沟道gates(Long channel-length)减小leakage,增加timing和area。

Cell library的model:

1)Timing model:完成multiple corner的synthesis,optimization。

2)Physical model:针对layout,包含power和signal ports。

3)Functional model:为了gate level的netlist simulation

4)Power model:分析dynamic和leakage的power optimization

5)Test model:支持ATPG和fault coverage。

针对multi-voltage,voltage scaling和power gating的design,传统的timing model变得不是太精确,

所以目前在后端多使用current source model(CCS)这样的模型来进行建模。

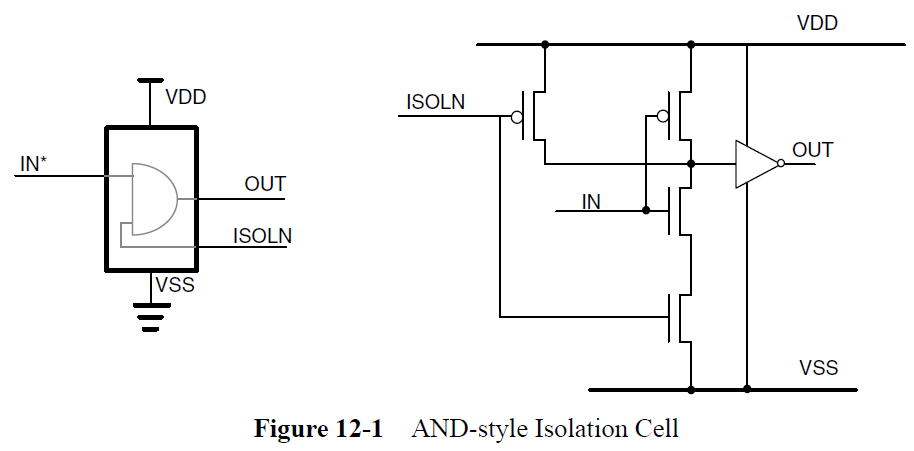

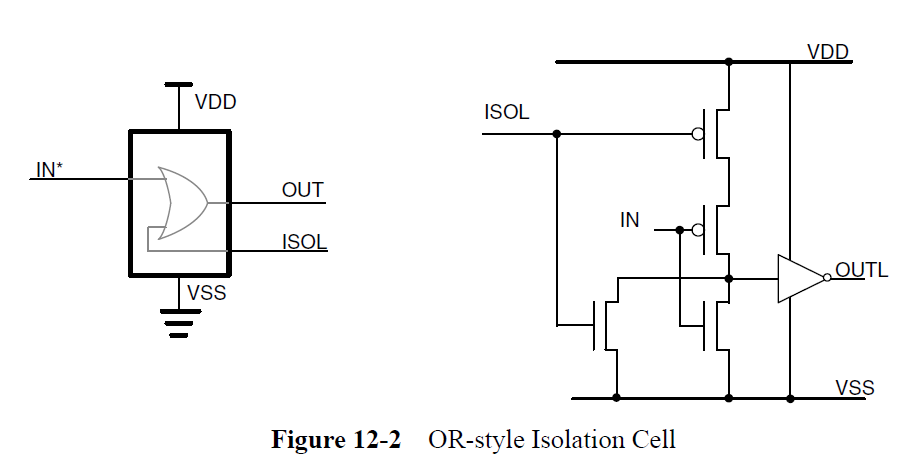

Isolation cell:主要实现有两种:

1)Power down domain输出的信号,进行isolate。

2)Power active domain输入的信号,进行isolate。

一般都使用Power down domain的输出信号进行isolate,因为:

1)当一个output signal输出到多个domain时,output的isolate只需要做一次,而input需要每个domain做一次。

2)output isolate,可以共享一个控制信号,而input需要做多个控制信号。

使用output isolate有一个缺点,iso_ctrl必须是aon的信号,所以在power rail上需要做特别处理。

而input isolate,iso_ctrl可以使用和domain一样的power rail。

信号的isolate分类三种:

1)clamp到"0", 2)clamp到“1”, 3)clamp到last值。

isolate的控制信号一般都是一个跨power domain的global信号,属于always-on的domain。

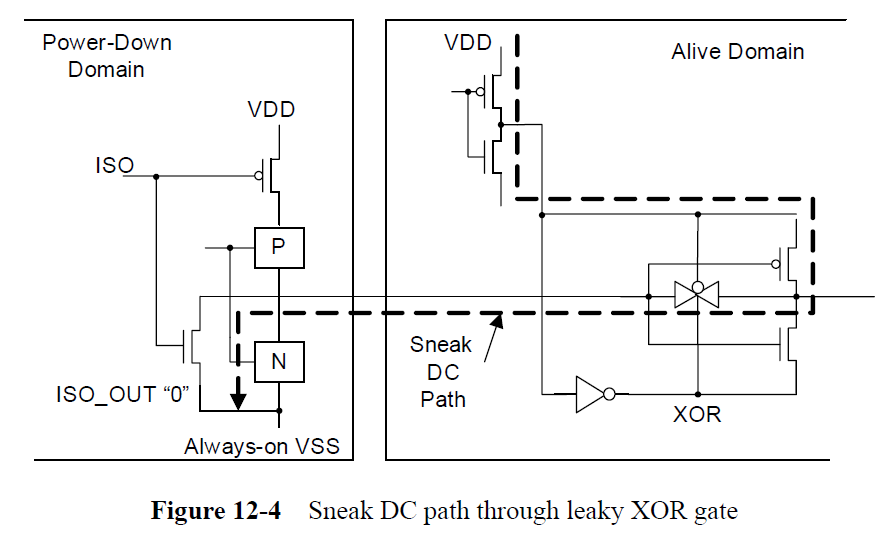

isolate cell外接一个门电路时,一般会带来sneak path leakage。从VDD到VSS的一条DC path。

总之:output signal isolate会比input isolate更好一些。

如果lib中的isolate cell不可用,使用门电路(AND,NOR)也可以自己搭建。

pass-gate logic不应该放在两个power domain的interface上,防止sneak DC path。

在placement和physical synthesis中,应该将isolate cell放在power island boundary上。

isolate cell会带来delay,所以不用的地方,尽量不用