Pswitch = Ceff * Vvdd^2*Fclk,

Pshort-circuit = Isc * Vdd * Fclk,

Pleakage = f(Vdd, Vth, W/L)

尽管对电压的scaling,可以以平方的关系减小dynamic/leakage power,但是voltage的scaling会影响gate delay,

setup/hold timing,memory access time scale。

voltage 的dynamic scaling,在processor和multi media的sys中会有明显的作用。

但是每一个votage的产生,都需要一个regulator的配合,会造成设计的复杂。每一个votage的产生都需要额外的power rail,

造成power的浪费,所以一般都将voltage和frequency作为N个离散的pair来进行设计。

如何根据应用场景scenario,来决定voltage的大小是一个比较困难的事情。

可以通过FPGA的Prototype仿真来完成。

freq的降低,会使得处理时间增加,所以从任务处理方面来看,并没有节能,

主要是因为电压的降低不支持那么高的Freq,所以需要进行scaling。

常见的几种voltage scale的技术:

1)static votage scaling(SVS):不同的block和sys,给不同的fixed voltage。

2)Multi-level votage scaling(MVS):一个block和sys的voltage可以在几个不同值之间switch。

3)Dynamic voltage and Frequency scaling(DVFS):工作电压根据workload进行动态的调整。

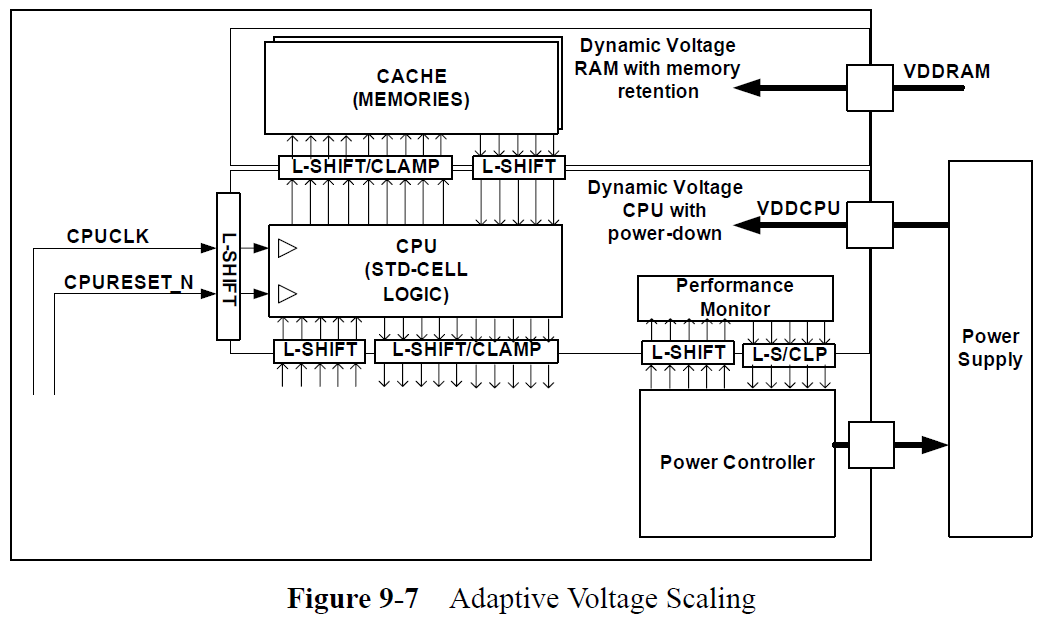

4)Adaptive voltage scaling(AVS):一个闭环的电压调节控制。

针对DVFS来说:

在需要增加Freq,over drive的情况下:软件首先决定最小的clock frequency,再决定最小的voltage供应。

1)cpu program power supply to new voltage。(cpu可以换为其他逻辑)

2)cpu继续工作在现有freq,直到voltage稳定。

3)cpu program新的freq,可以是clock divider或者PLL,如果是PLL,则需要花费更多时间等待PLL稳定。

如果是要降低Freq,则执行顺序:

1)cpu program新的freq。

2)等待clock divider或者PLL稳定。

3)cpu program新的voltage。

总之Freq只有在voltage增加之后,才能提高,Freq必须在voltage减小前,先降低。

针对timing/voltage的value。

很多的DVFS系统都设置一些discrete voltage/frequency pair。

如果pair太少,可能省电效果不好,太多可能造成decide逻辑冗杂。

可以根据:clock_divider可产生的值,voltage regulator的值来决定。

但是必须保证voltage的值在temperature inversion point以上。(一般情况下delay随着voltage的增加而减小,

delay随着temperature的增加而增加,但是,当voltage的值小于2Vt时,delay的值随着temperature的增加而减小)

(这个voltage的值不确定???)

voltage level的switch可能需要较长的时间,在做design时,可能需要加入counter等延时单元来等待。

如果Freq的scaling涉及到PLL,在relock有效之前,可以先利用别的clock保证logic的有效执行,在lock之后,进行切换。

DVFS是一个open loop的系统,通过frequency/voltage的预留margin来保证不同的PVT下,也可以正常工作。

但是AVS是一个close loop的系统,通过voltage scaling的power supply和delay sensing的performance monitor进行工作。

在DVFS block和剩下的sys之间,最好不要使用sync interface,因为电压的不同会导致clock的skew不同。

可以使用async逻辑或者latch