在IP的实现过程中,考虑lower power部分进行设计:

1)Partition the design来满足lower power的一些strategies,尤其是power gating和clock gating。

2)为power gating增加额外的逻辑。

3)设计clock和reset的strategy来配合lower power设计。

lower power memory可能需要好多mode:normal operating mode,retention mode,power off。

其中retention mode工作在一个低电压下,retain data。

针对power gating,在IP设计中需要注意:

1)区分power gating和power always on的block。

2)设计power controller控制power up和power down的sequence。(一般在IP外的一个aon模块中)

3)区分signal需要做isolate处理。

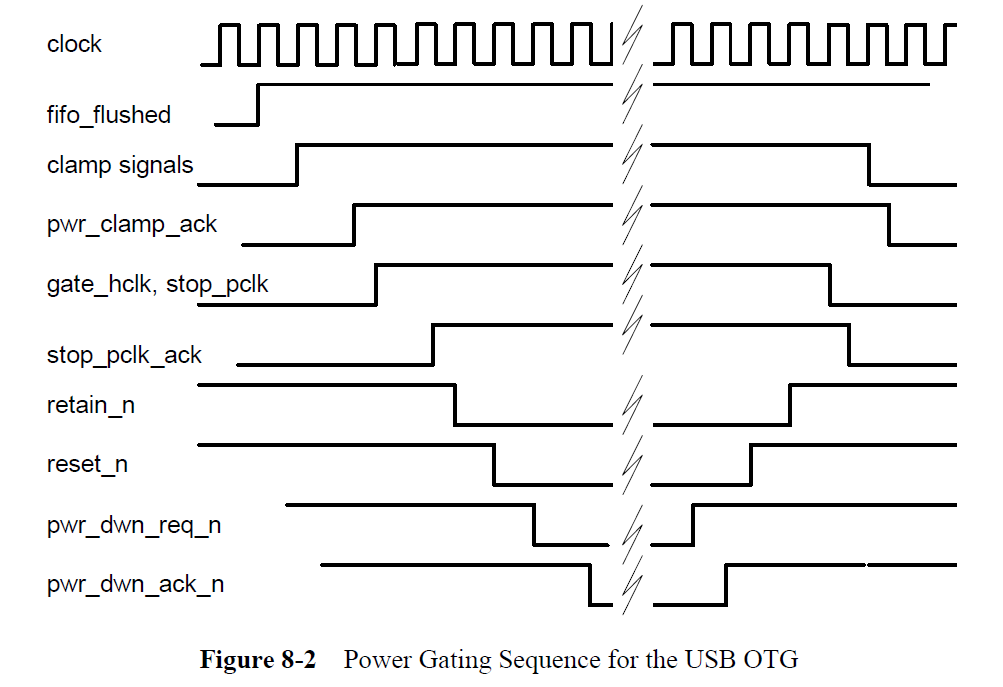

一般的power down和power up的sequence操作:

1)判断transaction和fifo都已为空。

2)停止clock。

3)针对isolate信号,进行clamp操作。

4)进retention操作。

5)复位IP。

6)关掉power。

上电过程中,会在clock之前进行一个rst,在经过clock的sync之后,才会被撤销。 异步复位的rst端口是电平触发,可以保证rst的成功。

但是仿真器中的X->0行为不确定。 掉电区域的clock,必须有一个clock的eb信号默认为有效,这样在上电后,可以保证有clock。

但是clock的频率需要再用该clock或者其他有电的clock进行配置。

rst的sync,只在存在cdc issue的问题上才会做。 同一个clock group上的clock,不需要做sync,不存在相位差。

上电过程中很多其他的clock的enable信号也必须是默认有效的,或者bus上的clock的enable信号默认有效。

1)从pmu过来的rst会进行同步; 2)Bus相关的rst会由bus的clock来同步; 3)Module相关的rst会由自己的clock来同步;

在rtl的simulation过程中,在power down之后,force register的输出为X,来进行仿真。

在gate-simulation过程中,可以建立一个switching fabric的model来进行仿真,还可以得到power up/down时间。

一个power gating的IP的框图,其中的pwr_switch在综合后加入。