ARM处理器的工作状态:ARM处理器有两种工作状态。在程序的执行过程中,处理器可以在两种工作状态之间切换,并且不影响

相应寄存器中的内容。

ARM状态,此时处理器执行32位对齐的ARM指令;BX指令,当操作数寄存器最低位为0时,进入ARM状态。

Thumb,此时处理器执行16位对齐的Thumb指令。BX指令,当操作数寄存器最低位为1时,进入Thumb状态。

BX(Branch Exchange):BX Rn; ##其中Rn可以是R0-R15中的任意一个。指令通过将寄存器Rn的内容拷贝到程序计数器PC

来完成4Gbyte的地址空间的跳转。

在进入异常中断后,ARM内核会自动切换到ARM状态,在异常中断处理程序入口的是ARM指令,

退出异常之后,根据异常之前的CPSR的值,来决定当前时arm状态还是thumb状态。

ARM处理器总是从ARM工作状态开始的。

ARM处理器的7中工作模式:

USE模式:正常用户模式。

FIQ模式:快速中断模式,支持高速数据传输。

IRQ模式:普通中断模式。

SVC模式:Supervisor模式,操作系统保护模式,处理软件中断swi,reset.

ABT模式:数据,指令中止模式。

UND模式:未定义模式,支持软件仿真。

SYS模式:系统模式,运行特权操作系统任务。

除用户模式之外的6中模式称为特权模式,特权模式下,程序可以访问所有的系统资源,可以任意的进行处理器模式的切换。

用户模式下不能访问一些受操作系统保护的系统资源,不能直接进行处理器模式切换,需要由应用程序产生异常处理。

特权模式中,除系统模式之外的5种模式称为异常模式。

之所以称之为异常模式,是因为这些模式都有自己的寄存器组。而user和sys mode共用一组寄存器组。

FIQ要比IRQ的响应快很多,首先FIQ的优先级比较高,再次ARM的FIQ会有自己更多的寄存器(r8_r12),由ARM自动保存。

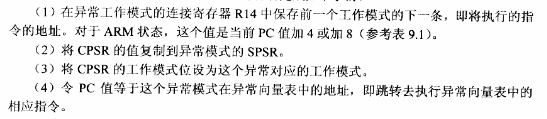

异常处理过程:将下一条指令存入LR寄存器,CPSR赋值到SPSR,强制设置CPSR运行位,跳转到异常处理函数。

返回:将LR中的值减相应的偏移量送到PC中,将SPSR的值复制到CPSR中。

异常向量表:0x0000_0000---复位Reset,进入SVC模式。

0x0000_0004---未定义指令,进入UND模式。

0x0000_0008---软件中断,进入SVC模式。

0x0000_000C---中止指令,进入ABT模式。

0x0000_0010---中止数据,进入ABT模式。

0x0000_0014---保留

0x0000_0018---IRQ中断,进入IRQ模式。

0x0000_001C---FIQ中断,进入FIQ模式。

异常与中断的区别和联系:

1. 中断可以看做异常的一种情况;

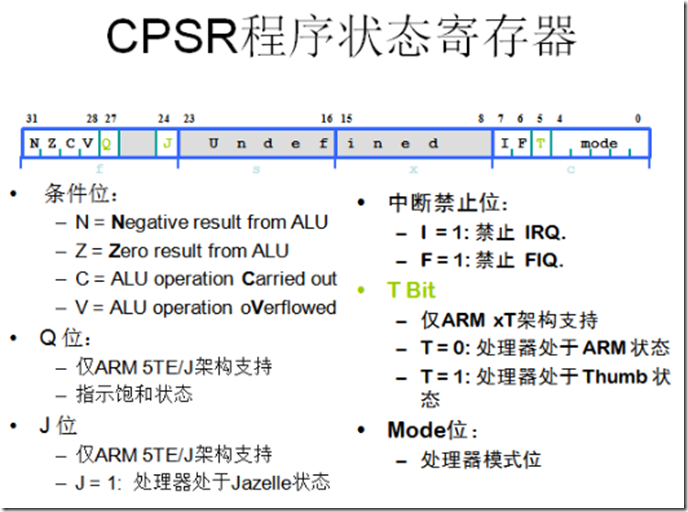

2. 中断是可以屏蔽的(CPSR的I位和F位分别屏蔽IRQ和FIQ),异常无法屏蔽。

3. 被动触发中断异常的情况会很多,中断异常指向的一般是中断向量表,根据中断ID在中断向量表中,找对应的中断服务子程序。

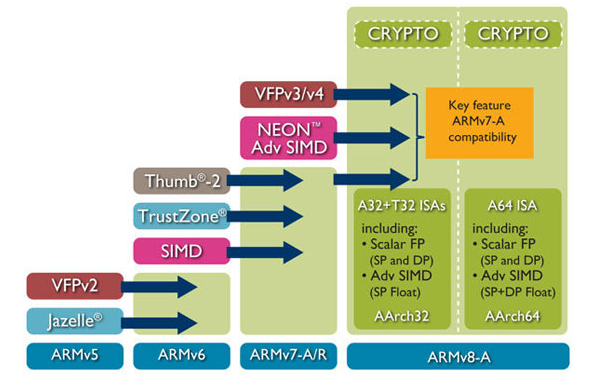

ARM的内核版本与对应的微处理器核心:

ARM7TDMI,ARM710T,ARM9TDMI,ARM920T V5

ARM11 V6

ARM Cortex-M,Cortex-R,Cortex-A V7

arm7是基于单纯的冯诺依曼结构来设计的,code和data共享总线,内部有三级流水线:取指,译码,执行;

arm9是基于哈佛结构来设计的,code和data分别有自己的addr和data总线,内部有五级流水线:取指,译码,取操作数,执行,写回。

arm7TDMI,arm9TDMI这样的内核并不能支持os,之后arm提供了加入mmu和cache的arm710t和arm920t内核的版本。

这样的内核版本中,即使有流水线操作也没有对分支进行预测处理,内核中的总线矩阵使用的是amba ahb总线。

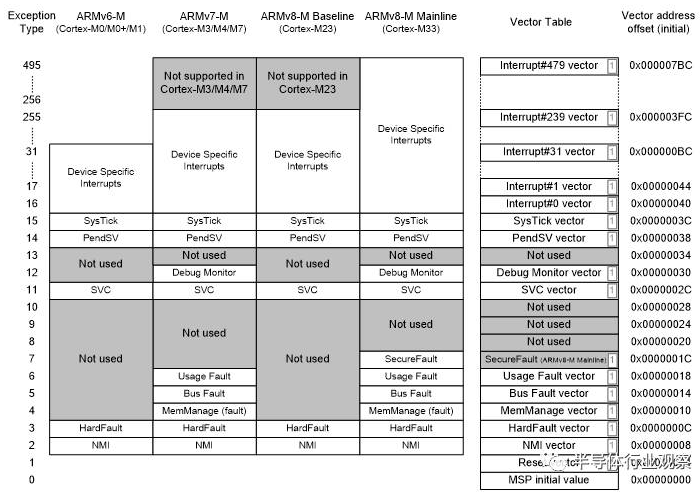

arm从armv7架构开始开发的cortex内核:

Cortex-M0,32位的,3级流水线mcu,内部是冯诺依曼结构,指令和数据共享同一总线,基于armv6m架构。

内部总线矩阵AHB总线,中断采用嵌套式中断控制器(NVIC),调试接口通过DAP接口支持jtag和swi。

Cortex-M3,32位的,3级流水线mcu,内部是哈佛结构,增加了分值预测功能。基于armv7m架构。支持thumb-2指令集,不支持arm指令集。

内部总线矩阵AHB总线,中断采用嵌套式中断控制器(NVIC),调试接口通过DAP接口支持jtag和swi,但是也支持coresight的部分etm功能。

支持MPU,存储器保护单元。内部实现了除法和单周期乘法的ALU单元。

Cortex-M4,在M3的基础上,增加了单周期乘法累加(MAC单元),SIMD指令,满足IEEE 754的FPU单元。同样不支持arm指令集。

Cortex-M7,总线矩阵使用amba4的axi 64bit,引入了data和code的TCM cache。

由于MCU中不会支持os,Cortex-M系列的异常模型,与A系列不同,处理器mode也相应的不同。

ARM处理器中一共有37个寄存器。

分别有31个通用寄存器:R0-R15, R13_svc, R14_svc, R13_abt, R14_abt, R13_und, R14_und, R13_irq, R14_irq, R8_frq----R14_frq。

6个状态寄存器:CPSR, SPSR_svc, SPSR_abt, SPSR_und, SPSR_irq, SPSR_fiq。

R13通常用作堆栈指针。R14通常用作子程序连接。

CPSR当前程序状态寄存器。SPSR备份程序状态寄存器。

arm处理器的架构发展:

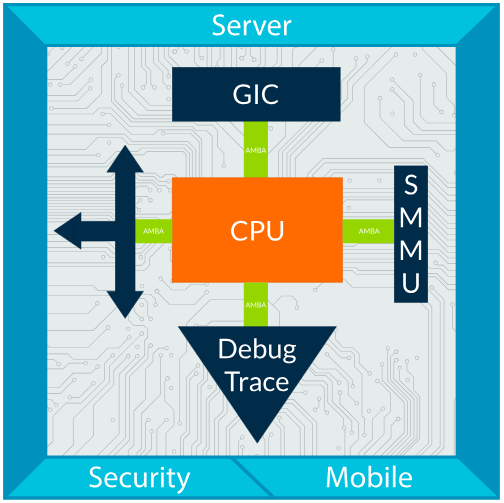

arm系统一般包括:mpcore,debug and trace,smmu,GIC,AMBA bus,security扩展,

arm中最多支持16个coprocessor,CP0-CP15,其中CP8-CP15是由arm reserve的,CP0-CP7是imp defined的。

arm的coprocessor model中,coprocessor一般包括,

1) 组成coprocessor interface的primary,secondary coprocessor寄存器;

2) internal寄存器;

ARMv7以及之前的版本中,包含的coprocessor有:

1) CP15,提供memory,cache,tcm的控制,和系统中非debug功能的寄存器;也被称为系统控制协处理器

2) CP14,提供其他系统寄存器的访问,包括debug,trace;

3) CP10,CP11,用作SIMD,VFP的控制,需要同时使用。

ARM的协处理器指令包括五个:

1) CDP,协处理器数操作指令,

2) LDC,协处理器数据加载指令,

3) STC,协处理器数据存储指令,

4) MCR,ARM寄存器到协处理器寄存器的数据传送指令,

5) MRC,协处理器寄存器到ARM寄存器的数据传送指令,

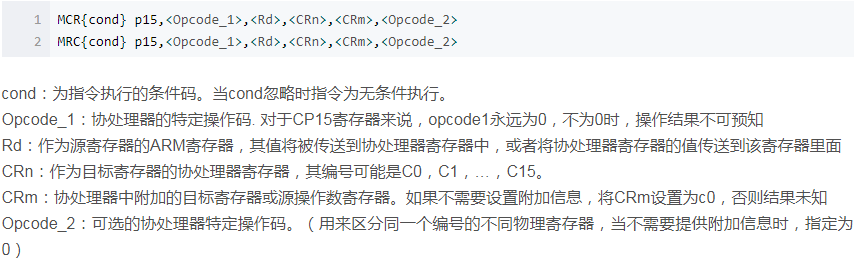

命令格式: